采用良好设计和板面布局让A/D转换器实现性能

出处:Robert Schreiber 发布于:2020-08-19 10:49:33

如何才能使 A/D 转换器实现 性能呢?明显的答案就是采用良好的设计和板面布局,除此之外,我们还可采用其他技术获得性能提升。我们实际上可采用一些简单的技术来推动 A/D 转换器性能,使之优于规范的要求。为了实现这一点,我们应了解 A/D 转换器误差的来源和类型。

本文的目的是解释 A/D 转换器 常见的误差源,并介绍进行上述误差补偿的方法。某些误差补偿的方法理解和实施起来都比较容易,而有些方法则不那么显浅易懂。如果采用方法得当的话,上述方法可大幅提高系统整体性能。

我们不妨先来看看理想的 A/D 转换器应该是什么样的,了解哪些类型的误差会阻碍我们获得 佳性能。简而言之,理想的 A/D 转换器会为我们提供几乎理想的数据。我说几乎是理想的,是因为即便理想的 A/D 转换器也存在量化误差,但我们不妨以后再讨论这一点。我们希望提高 A/D 转换器的性能,所以我们不妨先来看看市场上分辨率 的 A/D 转换器,即 24 位 A/D 转换器。

理想的 24 位 A/D 转换器可提供 24 位可用数据。这种 A/D 转换器可为给定输入提供相同代码或转换结果的输出,同样也受到量化的限制。例如,如果我们对输入范围为 5.0V 的理想的 24 位 A/D 转换器采用刚好 2.5V 的固定模拟信号,那么我们从 A/D 转换器所得的 代码就是8,388,608--标度值 (scale value) 的一半。如果我们对非理想转换器采用相同电压的话,那么输出代码不会固定为一半大小值,它实际上会给出不同的输出,是否稳定并不确定,这是由转换器的不理想特性造成的。不理想的 A/D 转换器会造成量化误差、偏移和增益误差以及非线性。此外,噪声和漂移也会导致测量误差。

即便是理想的 A/D 转换器也会发生量化误差。量化误差指数字化模拟输入信号时产生的误差。举例来说,输入范围为 5V,那么每个代码反映约 298 nV (5V/2^24) 的分辨率。如果我们开始时采用 0V 模拟输入电压,然后再逐步增加模拟输入电压,那么代码会保持零不变,直至达到 149 nV 或 ? LSB 左右进行 个代码转换。因此,即便采用理想的 A/D 转换器,我们仍会遇到 +/- ? LSB 的量化误差。之所以如此,是因为模拟输入信号在 0V 到 149 nV 之间可取一个无限数值,但数字代码只能为有限数值,理想情况下仅为 0。

我们常常一并考虑偏移误差和增益误差。偏移误差是指对 A/D 转换器采用零伏差动输入时实际代码与理想代码之间的差异。增益误差是指从负满量程转为正满量程输入时实际斜率与理想斜率之差。偏移和增益误差通常是 A/D 转换器中主要的误差源。

非线性包括整数非线性 (INL) 和差动非线性 (DNL)。整数非线性指出的是输出代码与理想输出之间差异的大小,而偏移和增益误差已得到校正。在满量程端点 (full-scale endpoint) 处取一理想线,一般来说,经测量得到的 INL 既为到这一理想线的 大偏差。差动非线性是指代码值如何随模拟输入的变化而变化。就模拟输入电压的升高情况而言,代码可能增加、不变或减少。根据模拟输入增量的多少,代码应该保持不变或者增加。如果出现这种情况的话,那么 ADC 就是单调性的。如果 ADC 跳过一个输出代码,那么此代码称之为缺失代码。如果代码输出减少,那么我们就说 ADC 为非单调性。通过查看柱状图,我们可以得知是否存在缺失码,以及关系代码宽度的大小等。如果分配正常而无缺失码,那么这就表明代码宽度一致。

噪声是随时间变化的随机输出代码,与偏移、增益和线性误差无关。即便我们已经很好地校正了A/D 转换器的所有其他误差来源,我们仍会发现由于噪音的缘故出现输出代码变化。

漂移是指在给定输入的情况下输出代码随时间或温度的变化而进行的变化。如果我们采用固定的模拟电压,然后给设备加热或去热,输出代码就会随着温度而进行偏移。根据设备特性的不同,在给定的抽样中漂移可能向相同方向发展,也可能呈随机性。

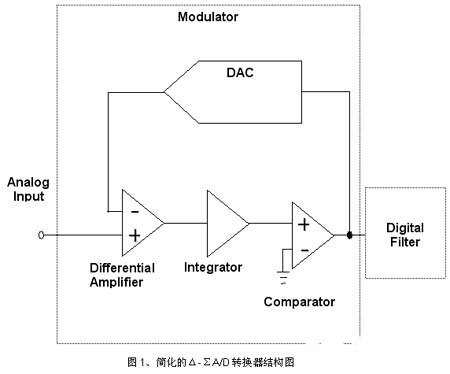

尽管难以对所有误差来源进行可视化,不过我们可通过芯片级设计技术或数据处理技术来解决这些误差来源。在我们详细了解如何补偿误差源之前,不妨先来了解一下A/D架构。在分辨率大于16位时,我们广泛采用 Δ-Σ 架构。Δ-Σ 架构采用重复采样技术来实现高分辨率数字输出。图 1 给出了简化的 Δ-ΣA/D 转换器结构图。A/D 的主要组件是调制器和滤波器。调制器作为反馈环路环路工作,其目标是将差动信号误差驱动为零。我们通过微差测量模拟输入信号和反馈DAC信号来实现这一目的。Δ-Σ 架构中的Δ(delta) 因此得名。上述二者之差或信号误差结合或合计到下 。Δ-Σ 架构中的西格玛由此而来。将总误差与参照信号相比较,从而相应地设置比较器的输出。如果误差项为正值,则反馈 DAC 输出升高,以尝试减小差动误差项。如果误差项为负值,那么反馈DAC 输出则降低,以尝试减小差动误差项。比较器 1 和 0 的密度与模拟输入电压成正比。

上述架构非常适用于高分辨率应用,因此我们不妨看看上述架构中各种类型的误差源是如何暴露出来的。

我们可通过采用噪声整形技术使Δ-Σ架构中的量化误差达到 小。噪声整形技术不会减小或消除量化噪声;它只是将量化噪声推向更高频率、使之不再影响有关频率(低频)而已。因此,就量化噪声而言,Δ-Σ架构的设计可以将量化噪声的影响降至 低。

Δ-Σ架构中存在偏移和增益误差,这与任何其他数据转换器的情况一样。此外,正是因为与任何其他数据转换器的情况一样,因而我们也可以通过简单的校准技术将上述误差 小化。为了进行偏移校准,我们采用 0V 或非常小的信号并读取输出代码。如果结果为正,那么转换器就存在正偏移误差,我们从结果中减去偏移值;如果结果为负,那么转换器就存在负偏移误差,我们就向结果加上偏移值。

我们通过对A/D转换器施加满量程或近于满量程的信号并测量输出代码来实现增益校准。偏移校准在增益校准之前进行。如果作图显示A/D转换器的所有输出代码的话,我们看到增益误差与理想输出代码斜率产生偏离,因此增益修正只不过是调整这条线的斜率而已。

INL存在于Δ-Σ架构中,就像任何其他数据转换器一样。但是,我们可以通过后处理数据对它进行补偿。从理论上说,INL 可以逐个代码地进行校准,但这是不实际的,因此通常我们选择一些数据点来校正 INL。我们通过对表进行线性化来完成上述工作。

DNL通常对Δ-Σ架构而言不是问题。就其特性而言,反馈环路中1位DAC输出是线性的,因此架构不调整也能获得优异的DNL性能。

任何电子设备都存在噪声,无法消除,但我们可以讨论采用何种方法来减小这种误差源。

任何电子设备都存在温度漂移,无法消除,不过,如果可以预计漂移的话,那么我们就能通过线性化表来补偿其影响。我们可通过温度监测来实现上述目的。此外,我们还能很准确地确定漂移对系统性能的限制。

因此,总而言之:我们可通过噪声整形技术来控制Δ-Σ架构中的量化误差,通过校准来 小化偏移和增益误差,采用线性化来改善 INL,而 DNL 则几乎不存在,噪声可 小化,而漂移则可纠正,其影响也可以估计。

小化噪声要比偏移和增益校准复杂一些。电子电路中有许多噪声源:热噪声、1/f 闪烁噪声和突发噪声。在 小化噪声方面,噪声类型非常重要。热噪声从本质上说是高斯型的,因此我们可采用特定技术来 小化其影响。闪烁噪声和突发噪声从本质上说是非高斯型的,因此上述技术对处理这种噪声源没有效力。

我们在评估噪声前,不妨先来看看噪声与分辨率之间的关系。噪声和分辨率相互关联,彼此定义。噪声可定义为输出代码与理想代码间的随机偏差。通常噪声的表现形式是伏特、代码、数量或PPM,而分辨率单位通常为位数或 dB。为了说明这一点,我们不妨假设理想的 24 位 A/D 转换器具有5V模拟输入范围。显然,分辨率为24位,因为这是理想情况。如果我们用 dB 来反映分辨率的话,那么分辨率就是6.02 * N dB(这里的 N 是位数),即 144.5 dB。我们通常称这种定义为信噪比。如果我们用代码来表示噪声,那么噪声就是一个代码。如果我们用计数来表示噪声,那么它就是 16,777,216 次计数。如果我们用伏特来表示噪声,那么它就是 (1/16,777,216) * 5V,即 298 毫微伏。如果我们用 PPM 来表达噪声,那么它就是 1/16,777,216 PPM,即 0.06 PPM。

这提出了另一个问题,非理想A/D转换器的分辨率如何定义?“有效位数”(ENOB) 和/或“有效分辨率”等术语通常用于定义A/D转换器的可用分辨率,如果考虑到设备的噪声限制的话。为了有助于理解分辨率和“有效分辨率”或ENOB之间的区别,我们不妨先看一下理想的12位A/D转换器。理想的12位A/D转换器有4,096个代码,也就是说分辨率为244 PPM。如果将模拟输入转换为数字值时我们强制给转换器结果增加12位分辨率,那么我们就可以说我们获得了24位分辨率的A/D转换器。实际上只有12位有用。上面的例子可能并不像您想像的那么极端。例如,市场上实际销售的A/D转换器就号称是24位A/D。在大约 25 Hz 的数据输出速率时,其噪声约 0.4 PPM,就其本身而言是相当不错的。但是,0.4 PPM的噪声意味着只有大约21.3位的有效分辨率。谁动了我们的24位分辨率?此外,如果您提高采样率,那么噪声可能会超过 600 PPM,这就使其甚至比 12 位 A/D 还糟糕!

有没有可能实现真正的 24 位性能呢?答案是肯定的。不过我们要做好准备工作。幸运的是,我们可用各种技术来减小A/D转换器的噪声。此外,如果我们系统有干扰的话,那么我们也可采用类似的技术来减小或消除它。从本质上说,我们可使 A/D 转换器获得更高的实际分辨率位数,从而实现更高的整体系统性能。这就是综合各种技术的优势所在。

为了实现更高性能,我们必须了解 A/D 转换器功能有多强。一项确定 A/D 转换器性能的广为采纳的技术就是进行柱状图分析。柱状图可清楚地告诉我们A/D转换器在DNL、DC偏移和噪声方面的情况。柱状图显示了输出代码和输出代码出现次数之间的对比情况。从柱状图测试中,我们可评估出代码宽度或容量大小 (DNL)。通过将输入接地,我们可能评估出噪声方面的信息。如果A/D转换器DNL较好,噪声为白噪声,那么柱状图就应类似于高斯型或正常分布。如果代码宽度小,那么代码出现的就少;如果代码宽度较大,那么代码出现就较多。如果代码不出现,那么就表明代码缺失。柱状图分析能够成为一种非常强大的工具。我们可方便地了解 DNL 性能和噪声特性。

如果柱状图显示 DNL 性能较好,分布也正常,那么我们就可假定噪声为白噪声。由于我们观察的是Δ-ΣA/D 转换器,因此从定义而言差动非线性应足够。ADS1252 Δ-Σ A/D 转换器的数据采样柱状图为 32,768,这表明 DNL 性能近于理想情况,而输出代码分布与正常分布很类似。因此,我们可以假定该 A/D 转换器的噪声为白噪声。这意味着我们可使用统计学方法来评估噪声。

如前所述,如果A/D转换器数据有一般的特性模式,那么我们可将数据集放入一般模式中。一般模式通常是指概率分布。由于数据表现出白噪声特性,因此我们可用高斯机率密度函数来评估噪声。函数显示了信号超出特定值的可能性,如以下方程所示:

这里:

u =真实平均数

x =信号值

s =标准偏差

从该方程式可看到,随着 x 从平均值移开,可能性降低,而输入信号会超过给定值。使用该方程式,我们可实际计算信号在给定时间内处于特定范围的可能性。

因此,我们可采用高斯几率密度函数作为数据模型。下一个问题就是我们的模型到底有多好?我们用两种标准统计原理来解决这一问题。首先,平均法则指出,如果总体存在一个真实的平均数 (u)且x为总体中n个个体随机采样的采样平均数,那么随着n不断加大,采样平均数 (x) 也会越来越接近真实平均数 (u)。由于我们讨论的是白噪声的情况,因此采样平均数会与真实平均数很接近,前提是采样规模足够大。因此,我们知道我们可以信任计算得出的真实平均数 (u),因为它与真实平均数 (u) 有关。

我们如何了解标准偏差计算得到底好不好?我们可用中心极限定理来回答这一问题。该定理指出,如果总体具有真实平均数 (u) 和真实标准偏差 (s),那么总体中n个个体所有可能的采样平均数集合的概率分布就会随n的增大越来越接近平均数 (u) 和标准偏差 (s/sqrt n) 的正常分布。从根本上说,如果我们采样更多的话,那么我们就能减小标准偏差。

如果我们完全依赖中心极限定理,那么我们可采用越来越多的采样,从而使标准偏差越来越小。不过改善的速度不会太快。采样数量增加实现标准偏差改善也有一个限制。一旦采样数超过了这个限制,那么您就不会再得到任何好处,甚至还会增加标准偏差。采样数量有限制的理论建立在方差的基础之上。方差理论广泛用于评估信号源的频率稳定性,不过它适用于任何采样系统。换言之,系统稳定时采样只会降低标准偏差。稳定性受许多因素影响,包括随即事件,甚至系统中的漂移。

对于主要包括白噪声的系统而言(与我们这里讨论的系统类似),平均方差是标准方差的测量方法。在这种类型的系统中,我们可采用方差来预计标准方差。通过使用方差,我们可实际预计采样对系统的影响。从根本上说,方差分析之所以起作用,是因为我们收集了大量采样并分析采样数量上升时方差如何变化。方差 小时的采样数量就是我们给定系统的 佳采样数量。这是一个非常有用的工具,有助于我们快速而方便地优化采样技术,从而获得 大的系统性能。

我们不妨将理论运用到实际的 24 位 A/D 转换器来进行检测。我们前面提到的 24 位 A/D 转换器在25 Hz 采样率上噪声约为 0.4 PPM。将 PPM 转化为位数,我们可评估应当如何对 A/D 转换器进行采样以获得期望的性能。在 PPM 和位数之间相互转化的方程式如下所示。

在 PPM 与位数之间相互转化的方程式

应用以上方程式时,为了获得 24 位分辩率,我们需要将噪声降低至 0.06 PPM。这就是说,我们必须使噪声减少几乎 7 个值才可以。根据中心极限定理,我们需要采用约 49 个采样来实现上述噪声性能。不幸的是,这会让我们的采样率降至约 0.4 Hz,而我们的信号带宽(-3dB 频率)则降至约0.1 Hz。这种采样率不仅对于许多应用而言太慢了,而且信号带宽也会对性能造成灾难性影响,因为输入信号的任何变化都会对建立时间造成极大影响。我们能够以更快的采样速率运行 24 位 A/D,但有效分辩率的降低造成的问题比信号速率还严重,因此我们追求高速度反而会使问题恶化。

幸运的是,我们可以找到解决该问题的方法。ADS1252是一种采样频率为 40 kHz 的 24 位 Δ-Σ A/D转换器。如果有效分辩率在 40 kHz 速率上足够高,那么我们就可获得足够的分辩率,能够对数据进行采样以提高分辩率,并仍然可获得足够的采样率。我们不妨来看看 ADS1252 的规范性能,其在 41,667 Hz 数据速率上的噪声为2.5 PPM。根据中心极限定理,我们应采用 1,736 个采样来实现 0.06 PPM 的噪声,这时的数据速率为 24 Hz。从论文上看,我们已获得了解决方案。此外,由于我们的 A/D 运行时采用更快的采样率,从平均采样数来看,总滤波器衰减较慢。这意味着我们可获得更高的信号带宽。例如,我们早先谈到了带有 sinc3 滤波器的 25 Hz 的 24 位 A/D 转换器,其输出的信号带宽约为 6 Hz。采用平均数据的 ADS1252 的信号带宽约为 10 Hz,因此我们实际上提高了信号带宽。

为了弄明白该解决方案是否切实可行,我们收集了数以万计的采样,并采用平均和方差技术来检查是否确有效果。表 1 和表 2 给出了不同理论的噪声和分辩率比较。

表中数据显示了一些有趣的结果。方差分析与实验数据稳和很好;但是,实验数据与中心极限定理预计应得的结果则存在一定偏差。这很可能是由于系统干扰造成的。进一步分析方差显示,采样大于 12,000 没有任何好处。对超过 12,000 次的采样进行平均,实际上反而会降低噪声性能,因为系统因漂移而造成不稳定。因此,我们采用本方法可对系统性能进行优化。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 电表互感器匝数倍率怎么看?2025/9/5 17:05:11

- 颜色传感器原理及实际应用案例2025/9/5 16:09:23

- 调谐器和调制器的区别2025/9/4 17:25:45

- 有载变压器和无载变压器的区别有哪些2025/9/4 17:13:35

- 什么是晶体谐振器?晶体谐振器的作用2025/9/4 16:57:42