TI - 使用高速数据转换器快速取得成功的关键

出处:mouserBlog 发布于:2021-01-05 16:51:02

无论是设计测试和测量设备还是汽车激光雷达模拟前端(AFE),使用现代高速数据转换器的硬件设计人员都面临高频输入、输出、时钟速率和数字接口的严峻挑战。问题可能包括与您的现场可编程门阵列(FPGA)相连、确信您的 设计通道将起作用或确定在构建系统之前如何对系统进行 建模。

本文中将仔细研究这些挑战。

快速的系统开发

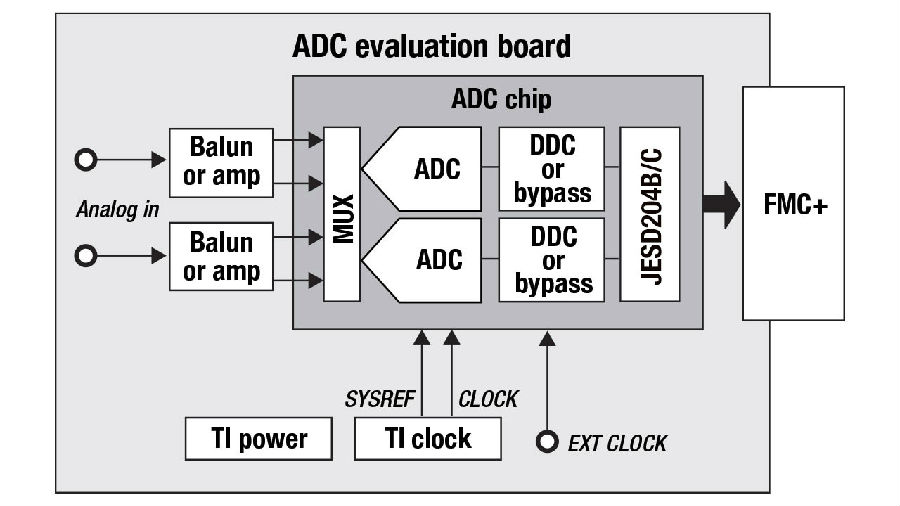

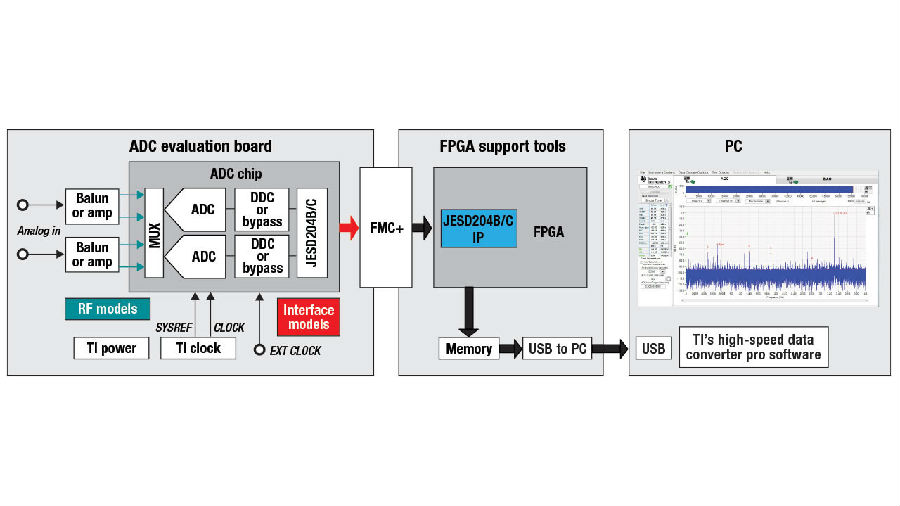

开始新的硬件设计之前,工程师经常会在自己的测试台上评估 重要的芯片。一旦获得了运行典型评估板所需的设备,组件评估通常会在理想情况的电源和信号源下进行。TI大多数情况下会提供车载电源和时钟,以便您可使用 少的测试台设备以及如图1所示设置的更实际的电源和信号源来运行电路板。

Balun或amp

Balun或amp

TI功率

TI时钟

DDC或旁路

DDC或旁路

ADC芯片

ADC评估板

模拟输入

系统参考

时钟

外部时钟

图1:典型的ADC评估板

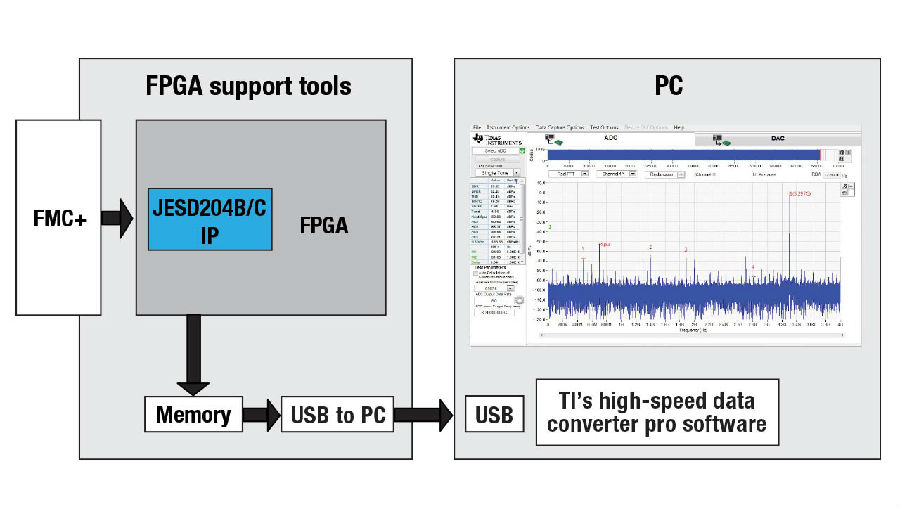

验证性能后,可将更完整的评估板的示意图和布局作为那一部分子系统的参考设计部分子。我们的数据采集和模式生成工具支持CMOS、LVDS和JESD204,并附带操作它们所需的软件。为您的高速数据转换器使用评估板用户指南,可在不到10分钟的时间内启动并运行大多数评估板。参见图2。

内存

TI的高速数据转换器 版软件

USB至PC

FPGA支持工具

图2:TI的数据采集和模式生成的硬件和软件

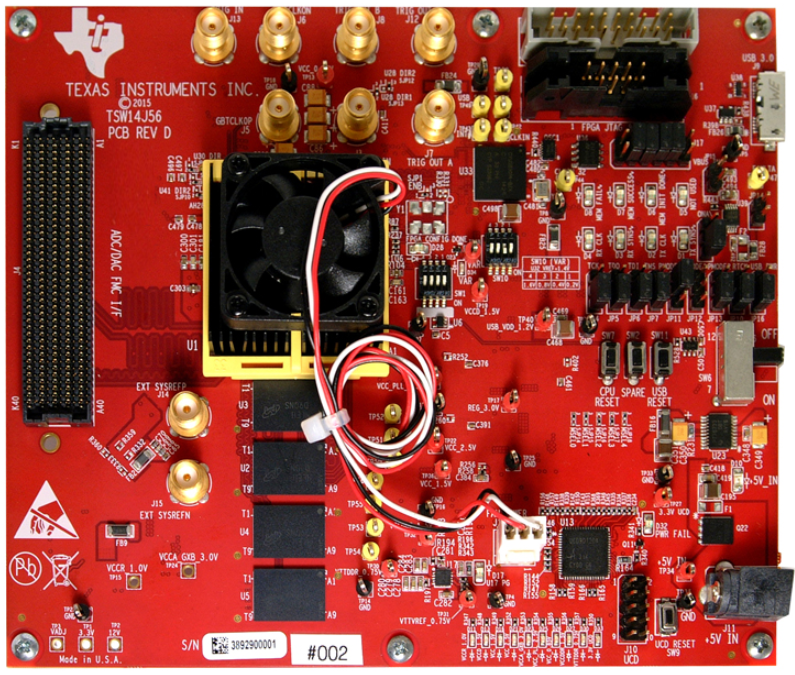

随着系统变得越来越复杂,您可能需要评估更广范围的用例。此时你可能会需要一块评估板。如果您的评估需求变得复杂,则可使用Python、MATLAB、LabVIEW或C ++软件通过设备评估板、采集卡解决方案和测试台设备直接与设备通信。我们支持板的一些很好的示例包括用于LVDS/CMOS的TSW1400EVM以及用于支持JESD204B串行器-解串器(SerDes)协议设备的TSW14J56EVM,如图3所示。

图3:TI的用于JESD204B数据采集或模式生成的TSW14J56EVM

TI还支持单台PC上的有多评估模块原型的完整系统级模型。例如,通过将KCU105或VCU118等Xilinx FPGA开发套件连接到多个模拟-数字转换器(ADC)或数字-模拟转换器(DAC),可同时测试发送和接收通道。

在线CTA:

加速从概念到原型的设计。

探索我们的JESD204快速设计IP,以简化FPGA集成并缩短总体开发时间。

FPGA连通性以及JESD204B和JESD204C

您可能要解决的 问题之一是如何在FPGA中获取数据。尽管LVDS和CMOS是简易接口,但它们在设备上每个管脚上支持的速度极其有限。随着更新型的高速数据转换器更普遍地支持> 1 GSPS的输入或输出速率,这些接口要么失去市场,要么使设计变得复杂。

为微电子行业制定开放标准的JEDEC创建了JESD204,通过支持超过12.5 Gbps的差分对通道速率来解决此问题。但尽管JESD204 限度地减少了管脚数量,但它通过对并行数据进行编码和串行化或反序列化和解码增加了接口复杂性。

到目前为止,您不得不主要依靠JESD204知识产权(IP)块和FPGA供应商提供的支持。尽管这些IP块可很好地工作,但它们以支持任意配置的任何设备的方式提供。这意味着很难为您的特定用例进行了解和配置。您需要花费大量精力自己设计IP,或从第三方IP提供商那里寻求IP。但如果出现问题,第三方IP将需要在实现方面提供帮助和支持。

TI自有的JESD204快速设计IP可针对您的FPGA平台、数据转换器和JESD204模式进行预配置和优化。我们的IP需要更少的FPGA资源,同时还可针对每种特定用途进行定制。另一个优点是实现JESD204链接仅需数小时或数天,而非数周或数月的时间。

设备模型

随着直接射频(RF)采样和超快SerDes与高速数据转换器的结合变得越来越普遍,对RF和信号完整性进行建模的能力已成为成功通过首次设计的必要条件。传统上讲,大多数供应商仅为S参数模型中的ADC提供输入阻抗信息,但TI的ADC12DJ3200、ADC12DJ5200RF和ADC12QJ1600-Q1高频输入器件的目标是高达8 GHz的采样频率,现在具有包含阻抗和频率响应信息的S参数模型。

使用此新模型,您可模拟预期的设备行为并优化阻抗匹配。TI的策略是在支持极高的输入和输出频率的设备上提供这些模型,而阻抗匹配和实现所需的频率响应则更具挑战性。

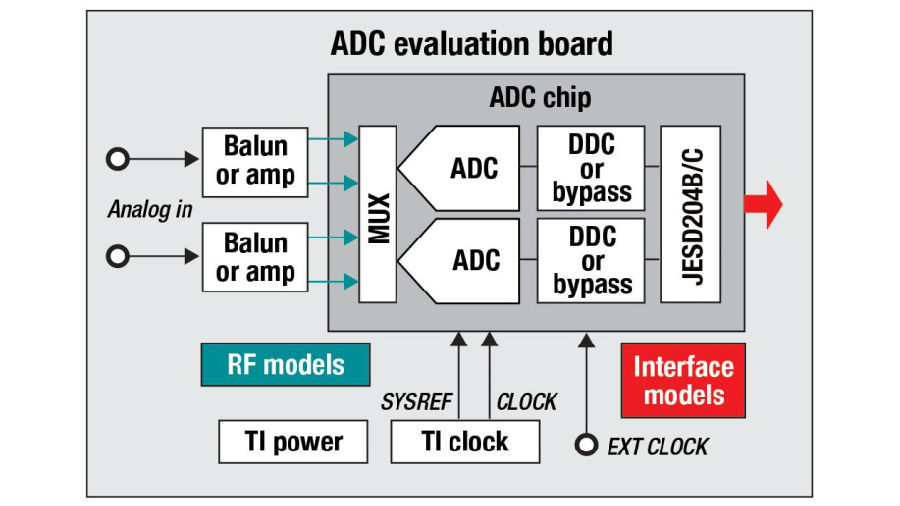

在数据转换器的数字接口侧,输入/输出缓冲区信息规范(IBIS)是一种通用模型,可为CMOS和LVDS管脚提供物理层信息以及DC和AC类型的行为。对于大多数使用高速JESD204 SerDes的新型数据转换器,这些模型已改进为IBIS-算法建模接口(AMI),其中包括有助于应用均衡和预加重或后加重的有用信息。IBIS-AMI提供您所需的建模功能,使您首次即可正确使用电路板,同时实现良好的误码率、信号完整性和稳健的数据链路。图4所示为RF(绿色)和数字接口(蓝色)模型。

Balun或amp

Balun或amp

TI功率

TI时钟

DDC或旁路

DDC或旁路

ADC芯片

ADC评估板

模拟输入

系统参考

时钟

外部时钟

RF模型

接口模型

图4:接口建模

结论

无论您使用高速数据转换器进行设计已有一段时间,还是对高速设计还不太熟悉,都不用担心,因为TI正设计易于使用的高速数据转换器。我们构建了一个可简化所有工作的完整开发环境,如图5所示。

利用可轻松实现FPGA集成的现成IP、 的RF系统模型以及市场上稳健的一组灵活、可扩展和可自动化的评估模块,您可缩短几个月的固件开发时间、减少昂贵的设计周期并加快从概念到原型的高速设计。

Balun或amp

Balun或amp

TI功率

TI时钟

DDC或旁路

DDC或旁路

ADC芯片

ADC评估板

模拟输入

系统参考

时钟

外部时钟

RF模型

接口模型

内存

TI的高速数据转换器 版软件

USB至PC

FPGA支持工具

图5:典型的高速模拟-数字转换器(ADC)评估环境

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 低通滤波器和高通滤波器的区别图像处理2025/8/7 17:04:34

- 一文看懂电流互感器选型原则和方法及使用方法2025/8/7 17:00:36

- 陀螺仪是什么,它的工作原理是什么?2025/8/6 11:39:27

- EMI 滤波器应用揭秘:实现和谐 “共舞” 的秘诀2025/8/6 11:08:06

- 整流二极管反向恢复过程全解析2025/8/6 10:42:32