将 FPGA 嵌入 DSP 驱动的软件无线电应用中

出处:维库电子市场网 发布于:2023-07-26 15:59:37

现场可编程逻辑一直是连接宽带 A/D 和 D/A 转换器、数字接收器和通信链路等高速外设到嵌入式实时系统中可编程处理器的电路。

FPGA(现场可编程门阵列)特别适合处理时钟、同步以及驯服这些专用设备所需的其他各种定时电路。此外,FPGA 非常适合数据格式化任务,例如串并转换、数据打包、时间戳、多路复用和数据包形成。

但它们的 DSP 功能已成为 FPGA 固有的重要功能之一,过去几年 FPGA 供应商对该技术的工程和营销投资急剧增加就证明了这一点。

数字信号处理任务

在传统的软件无线电接收器系统中,经过转换和滤波的基带信号作为时域波形的复杂样本流发送到 DSP。DSP 必须处理所有解调任务以及基于接收信号分析的更别决策。

信号智能接收器通常通过首先对信号进行频谱分析来估计使用的调制类型来对信号进行分类,然后应用解调算法来确定是否提取了有用的信息,例如可理解的语音或有意义的数据。

DSP 的其他重要任务包括解密、数据存储、通道切换、到其他系统的信号路由、记录??活动以及向操作员发送音频或数字数据以供收听或显示。

在手机基站中,数字信号处理任务的数量随着每个新通信标准的增加而增加。复杂的数字语音和数据协议的激增需要解码、卷积、成帧、纠错和声码。

采样率要求的稳步增加加剧了这些额外任务的处理负载。为了支持宽带 CDMA 等新应用,DSP 距离天线越来越近。

为了满足这些需求,DSP 时钟速率已增加到 200 MHz 以上,并且许多新器件具有两个或更多硬件乘法器。然而,作为系统中昂贵、耗电的资源之一,限度地减少 DSP 的大量工作负载显然非常重要。

FPGA 在 SDR 中的作用

在过去五年中,为了适应 DSP 功能,FPGA 在几个关键领域取得了巨大的进步。这些器件的栅极密度很好地遵循摩尔定律,大约每年半增加一倍。近发布的一些设备号称拥有 1000 万个门!门阵列通常被构造为配备存储器并能够执行数学函数的逻辑单元。这些高密度逻辑单元现在可用于各种基本“”,以支持快速乘法器、用于处理 FFT 处理的块存储器以及用于 FIR 滤波器的分布式存储器。

FPGA 综合工具现在支持“可参数化”内核,这些内核接受位宽定义并自动生成内核结构以满足信号处理精度要求,而不会浪费门。

现在可以使用多种前端设计工具来满足硬件和软件系统工程师的各种输入偏好。其中包括框图系统生成器、原理图处理器以及用于 Verilog 和 VHDL 的输入语言编译器。新模拟器的速度、准确性和易用性简化了新设计的测试,并限度地减少了调试应用程序所花费的时间。

第三方供应商现在提供 IP 内核,以补充 FPGA 供应商提供的标准内核。这些范围从完整的 DSP 处理器到高速互联网调制解调器等特定应用模块。凭借这些新的商业“现成”功能,FPGA 现在能够打入通用 ASIC 市场以及 DSP 市场。

更重要的是,FPGA 的数字信号处理能力通常可以胜过通用 DSP。例如,如果宽带 FIR 数字滤波器在单个时钟周期内需要 32 个 MAC(乘法/累加运算),则仅具有两个乘法器的通用 DSP 将远远达不到要求。另一方面,FPGA 可以轻松整合 32 个 MAC 内核来处理任务。

灵活且可重复使用

这种基于 COTS 的软件无线电系统是实现各种应用的理想平台。通过将新的 FPGA 设计工具和 IP 库用于这些高度可配置的基于 FPGA 的 COTS 板级产品,系统设计人员可以消除对定制板的需求。由于 FPGA“硬件”可以从根本上重新配置,无需新的电路板设计,因此当前项目中使用的相同产品可以轻松地重新配置以适应未来的应用。

随着新的软件无线电算法的开发,它们可以首先在 DSP 上进行测试,利用更广泛的代码生成、仿真和优化工具。完成后,该算法可以移植到 FPGA,以实现更好的实时操作或支持许多并行通道的处理负担。,为了过渡到大批量生产,大多数 FPGA 设计都可以轻松转换为定制 ASIC 的掩模工具。

虽然重新编程 FPGA 来处理新功能可能比为 DSP 编写新算法复杂一些,但这种努力程度的差距似乎正在缩小。FPGA 设计工具不再是硬件设计人员的专属领域,现在越来越广泛地被软件工程师使用,确保这一重大技术转变将代表未来嵌入式系统设计的主流范例。

软件无线电模块应用

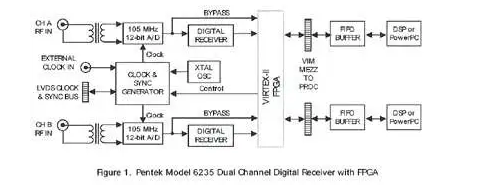

DSP 驱动的 FPGA SDR 平台的强大功能和灵活性的一个说明性示例(如下图 1 所示)是连接到四路 DSP 处理器 VME 板的双通道数字接收器子卡模块。它包含两个能够以高达 100 MHz 采样率运行的 12 位 A/D 转换器,以及两个可转换和过滤宽带数字化输入的选定部分的数字下转换器。

着眼于添加 DSP 功能,此类平台中 FPGA 的自然选择是 Xilinx Virtex-II 系列。XC2V3000 具有 96 个专用 18×18 乘法器模块和超过 200 KB 的块 RAM,可提供丰富的信号处理资源组合,甚至适用于一些更重要的应用。

在模块的基本工厂配置中,FPGA 仍然为板上的各种器件执行传统的定时、格式化和粘合逻辑任务。由于这些功能相对简单,因此仅消耗 6% 的可编程逻辑。这使得 94% 的逻辑块、所有 96 个乘法器以及几乎整个块 RAM 可用于添加 DSP 算法。

为了帮助展示这些未开发资源的力量,启动了一个工程项目来实施高性能 FFT 引擎。由于通信、雷达和信号智能系统都利用 FFT 进行跟踪、调谐和图像处理操作,因此 FFT 仍然是的处理器性能基准测试算法之一。

简而言之,FFT 接受输入时域样本块,并将其转换为输出频域样本块。由于计算相当复杂,它消耗了大量DSP处理资源,成为FPGA实现的主要候选者。

构建 FFT

执行 FFT 计算有效的方法之一是 radix-4“蝴蝶”算法的迭代。在每个蝶形内部,四个输入数据点乘以正弦表中的系数,然后组合起来产生四个输出点。重复这种蝶形运算,直到处理完所有输入点,四个,代表一个“阶段”。要实现 4,096 点 FFT,需要六级蝶形运算。

与传统可编程处理器相比,使用 FPGA 计算 FFT 的好处之一是可以同时计算大量乘法器。

在上面的 4,096 示例中,总共需要 60 个乘法器来并行实现所有六个 FFT 蝶形级。由于 XC2V3000 具有 96 个可用乘法器,因此很明显为什么 FPGA 通常可以显着优于仅具有两个或四个硬件乘法器的标准 DSP 处理器,特别是对于 FFT 等算法。

由于 FFT 本质上是一种面向块的算法,因此当可自由寻址的 RAM 支持快速访问所有输入和输出样本时,FFT 的运行效率。然而,这种随机数据可用性的理想模型与来自 A/D 转换器的顺序输入数据样本流相反。

幸运的是,FPGA 的可配置块 RAM 资源可以重组,形成一个存储器结构,将适当的样本并行输入蝶式引擎的四个输入数据存储器端口,从而解决数据可用性问题。这种专有的内存架构允许以连续的脉动方式处理后续输入块,以便所有六个阶段中的所有乘法器都可以始终高效地使用。

对于每个 FPGA 时钟周期,每个 radix-4 蝶形运算处理四个输入样本。因此,当FPGA处理时钟等于A/D时钟时,上述架构的运行速度比实时快四倍。通过合适的硬件复用方案,同一 FFT 引擎可用于处理四个输入数据流,而不是仅一个。

在此示例中,由于两个 A/D 转换器和 FPGA 的时钟频率均为 100 MHz,因此 FPGA 仅以一半容量工作。但只要付出一点额外的努力,引擎就可以设置为处理两个通道的 50% 输入重叠处理,以充分利用硬件。在这种情况下,每个 FFT 的流水线执行时间是惊人的 10.24 微秒!这比以 100 MHz 采样率收集 4,096 个输入点所需的时间快四倍,与实时执行四次 FFT 一致。

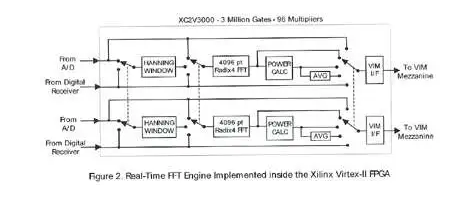

FFT 增强

由于 96 个乘法器中仅使用了 60 个用于 FFT 算法,因此结合了其他功能。在四个复数输入流中的每一个上,都可以应用一个可选的汉宁窗,需要八个额外的乘法器。由于 FFT 和 Hanning 窗的系数使用单独的 FPGA 表存储器,因此可以用替代输入窗函数代替 Hanning 窗。

另外八个乘法器用于在 FFT 输出处执行可选的功率计算,其中四个输出中每一个输出的实部和虚部进行平方,然后相加。,平均器级将 50% 输入重叠 FFT 的两个输出相加,以改善信噪比特性。

在 FPGA 的输出端,多路复用器允许将每个信号处理阶段的结果定向到处理器接口。下图2 显示了图1所示子卡模块的FPGA内部的所有基本功能块。

对于 4,096 点复杂 FFT,该 FPGA 引擎的执行速度为 10.24 微秒,其性能比在 400 MHz G4 PowerPC 上运行的优化 FFT 算法的基准高出十倍!

为了实现优于 90 dB 的计算动态范围,采用了多种技术来减少 FPGA 整数运算中固有的舍入和截断误差。通过部署可用的 FPGA 资源优化执行速度后,整个设计利用了 XC2V3000 器件 96 个乘法器中的 76 个、99% 的逻辑片和 97% 的块 RAM。

尽管这种特殊的 FPGA 组件由于近推出而仍然价格昂贵,但球栅阵列封装图案的两个同心子集可容纳同一系列中的两个较小的器件,从而为要求不高的应用节省成本。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 深入解析嵌入式 OPENAMP 框架:开启异核通信新时代2025/7/22 16:27:29

- 一文快速了解OPENWRT基础知识2025/7/14 16:59:04

- 独立 ADC 优势大揭秘:为何不可替代?2025/7/7 16:21:04

- 深入剖析:嵌入式中 RS485、RS422 和 RS232 的特点差异2025/7/5 15:07:54

- 揭秘嵌入式 MCU:浮点数据处理难点及应对策略2025/6/20 15:19:07