内存模块和其他内存子系统的支持逻辑

出处:维库电子市场网 发布于:2023-09-12 16:20:06

内存支持逻辑可用于通过解决抖动、传播延迟/偏斜和信号缓冲/驱动等时序问题来增强带宽。使用正确的寄存器和 PLL 可以进一步改善时序,在某些情况下(如 DDR1-400)甚至可以将内存技术扩展到超出其原始速度目标。

NXP 是一家成熟的内存接口供应商,提供全面的内存支持逻辑产品组合,其中包括注册命令和地址驱动器、PLL 时钟缓冲器以及适用于 PC100/133 SDRAM、DDR 和 DDR2 的 CBTV 总线开关。这些经济高效的解决方案提供标准和定制格式,在多种封装选项中提供行业的速度。

内存应用

注册双列直插内存模块 (DIMM)

使用 SDRAM、DDR、DDR2 技术的内存子系统

主板内存总线切换、缓冲和定时

终用户应用程序

服务器

图形和工作站

网络设备

电信设备

工业设备

NXP 内存接口解决方案

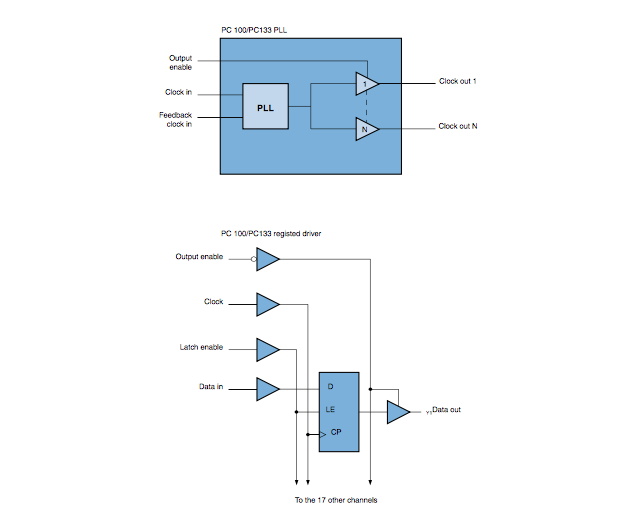

这种成熟的内存模块格式基于 3.3V 技术,使用具有单端 LVTTL(低压晶体管 - 晶体管逻辑)信号的 PLL 和寄存器,时钟速率为 100 或 133 MHz。通过使用 SDR(单数据速率)时钟(仅在一个时钟沿对数据进行时钟控制),相应的数据速率为 100 和 133 MT/s(每秒兆传输)。PLL 根据所??使用的存储器拓扑进行选择。非奇偶校验模块需要 9 个输出(8 个 DRAM 负载加 1 个反馈输出),奇偶校验模块需要 10 个输出(9 个 DRAM 负载加 1 个反馈输出)。所有寄存器都具有三态功能,并且为了支持特定的应用负载条件,都配备了内置串联终端电阻和动态控制输出

3.3V 典型电源电压

LVTTL信令

单数据速率 (SDR)

100 至 133 MT/s 数据速率

100 至 133 MHz 时钟速率

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- eMMC 属于闪存还是内存?从定义到应用讲透核心区别2025/9/15 15:24:16

- ddr4和ddr5内存接口一样吗?全景解析2025/9/8 17:22:03

- 虚拟存储器的概念和特征2025/8/4 16:49:21

- 铁电存储器和flash的区别2025/7/30 16:56:02

- 内存频率是什么_内存频率高有什么好处2025/7/29 17:07:27