LED 和检测器 IC 的热阻测量

出处:网络整理 发布于:2023-09-19 15:49:40

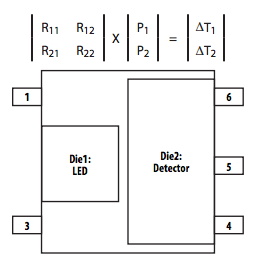

图 1 显示了组件框图。这是一种具有两个热源的多芯片封装,应用线性叠加理论考虑相邻芯片对一个芯片的加热影响。这里,首先加热一个芯片,并在达到热平衡后记录所有芯片的温度。然后,加热另一个芯片并记录所有芯片温度。有了已知的环境温度、芯片结温和功耗,就可以计算出热阻。热阻计算可以用矩阵形式表示。对于我们有两个热源的情况,这会产生一个 2 x 2 矩阵。

测量数据

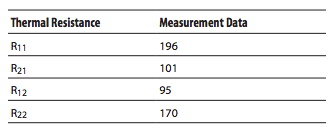

该封装安装在低电导率测试板上,根据 JEDEC 标准,该测试板的尺寸为 76.2 mm x 76.2 mm。包相对居中。总共准备了两个低电导率板用于测量。这些测试板由 FR-4 材料制成,铜迹线厚度符合低电导率板的 JEDEC 标准。所有板上都使用了经过测试的“良好”设备。所有热阻测量数据列于图 2 中。

上一篇:源测量单元仪器可以做什么?

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 频谱仪精准 TOI 测量的设置优化2025/9/5 16:39:30

- SiPM 测试板偏置电压源的选择与考量2025/9/2 15:54:57

- EMC的测试方法有几种常见2025/8/28 17:25:45

- FCBAG封装集成电路在失效分析中常用的检测设备与技术2025/8/27 17:03:25

- 高端精密装备精度测量的核心理论与实用方法2025/8/27 16:31:27