具有信号量仲裁功能的双端口 SRAM

出处:维库电子市场网 发布于:2023-10-13 16:51:08

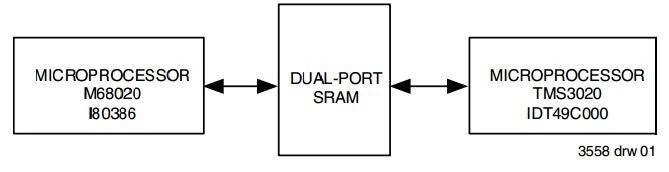

由于其高带宽和消息访问灵活性,双端口 SRAM 用于链接多个高性能处理器和系统。Integrated Device Technology 生产多种配置的双端口 SRAM,所有配置均由一个带有两组地址、数据和控制信号的 SRAM 组成。这允许两个处理器在各自的地址空间中共享同一物理内存块。两个处理器可以同时异步地访问两个内存位置中的数据。这种方法明显优于分立部件的设计,在分立部件的设计中,两个处理器必须通过仲裁来同步才能访问总线,该总线用于访问标准单端口 RAM 中的一个位置。

考虑一个多处理器系统,其中每个处理器都可以访问相同的数据。当多个处理器同时需要同一数据时,仲裁方案对于解决这种情况是必要的。解决仲裁问题的不同方法有不同的权衡,并且适合不同的应用。这些解决方案包括无仲裁、硬件解决方案、软件解决方案及其组合。

IDT71342 的功能描述

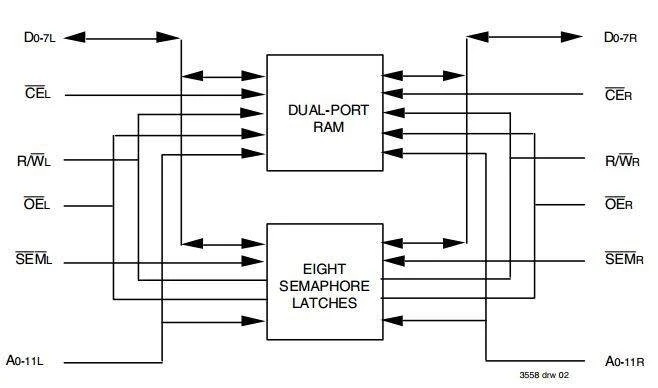

IDT71342 是一款具有信号量逻辑的快速双端口 4K x 8 CMOS 静态 SRAM,采用 52 引脚 PLCC 和 64 引脚 TQFP 封装。信号量逻辑可用于将双端口 SRAM 的部分分配到一侧或另一侧,并用于代替其他双端口设计中使用的地址仲裁逻辑。信号量由软件控制。因此,这种方法有几个缺点,包括分配任意大小的多个块以及没有处理器等待状态或繁忙逻辑。

信号量标志如何工作

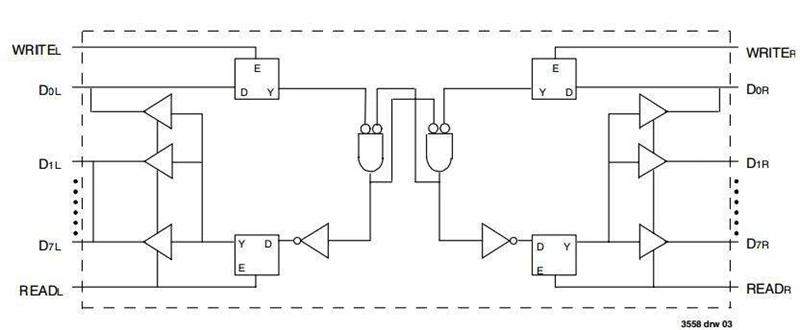

信号量逻辑由一组八个锁存器提供。这些锁存器可用于将标志或令牌从一个端口传递到另一个端口,以指示 SRAM 块正在使用中。内部电路防止标志同时在两个方向上传递。信号量为称为“令牌传递分配”的使用分配方法提供硬件辅助。在此方法中,信号锁存器的状态用作指示 SRAM 块正在使用的令牌。如果 Lport 上的处理器想要使用 SRAM 块,它会尝试设置请求令牌的锁存器。然后处理器检查锁存器以查看是否成功设置信号量。如果是,则处理器继续读取和/或写入该块。如果处理器未能成功设置锁存器,这意味着 R 端口首先设置了它,拥有令牌并且正在使用该块。L端口继续测试,直到成功,表明R端口已经释放了令牌,不再使用该块。

信号量为硬件和软件级别的各种问题提供了有用的解决方案。以下选择重点介绍了信号量的一些优点,从提高性能到提供其他设计所不具备的功能。

下一篇:了解共模信号

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 数字信号处理揭秘:载波调制的奥秘2026/4/29 15:12:09

- 数字信号处理揭秘:载波调制的深度解析2026/4/27 15:02:01

- 探秘硅光基础:有源铜缆在数据中心的应用2026/4/24 14:41:24

- 探秘 Δ - Σ ADC:简单 RC 抗混叠滤波的奥秘2026/4/24 14:28:17

- 全面了解 PLL:从原理到广泛应用2026/4/24 14:11:43