什么是GaN 器件外延

出处:维库电子市场网 发布于:2024-04-25 16:20:53

MOCVD 在 GaN 上的广泛应用直到 20 世纪 90 年代才开始,MOCVD 和 GaN p 掺杂方面取得了一些关键突破,促进了高亮度蓝绿光和白光 LED 的发展。蓝宝石衬底上低温缓冲层的开发以及 Mg-H 键的断裂以改善 p 掺杂是重要的进步。GaN MOCVD 面临三个关键挑战:

没有可用的晶格匹配衬底,需要大量工作来创建可以生长外延层的成核方案。

Ga 向表面的质量传输受到气相中发生的复杂反应的抑制。

没有好的p-掺杂剂可用。

这些挑战现已在很大程度上得到缓解,MOCVD 是 GaN 功率器件制造中使用的主要生长方法。

氮化镓外延

三甲基镓 (TMGa: Ga(CH 3 ) 3 ) 和氨 (NH 3 ) 作为 GaN 的化学原料,添加三甲基铝 (TMAl: Al 2 (CH 3 ) 6 ) 生成 AlN 和HEMT 所需的 AlGaN 异质结构层。液态金属有机物通常通过不锈钢起泡器输送,不锈钢起泡器被加热以提供合理的蒸气压。载气(例如氮气和氢气的混合物)用于将材料输送到生长室。可以使用两种基本类型的 MOCVD 腔室:

冷壁:这里的基板是热表面,而腔室保持冷。这些更常见,并且具有设计更简单和温度控制更好的优点。石墨/碳化物涂层衬底支架(基座)通常采用电阻加热。

热壁:整个室和基板被加热。这里的优点是前体化学物质的裂解更加有效,并且由于生长区域中的热梯度降低,在生长过程中可能会减少晶圆弯曲。这里石英室可以被感应加热。

沉积通常在50-100毫巴的压力下进行。生长应在层流气流下进行,以获得高均匀性,较低的压力可减少紊流的可能性。生长温度通常在 500 至 1,300 o C 之间变化。较低的温度会导致反应受限,其中生长速率对温度更敏感。较高的温度导致优选的质量传输限制区域,其中生长受到反应物通过边界层的扩散的限制。由于解吸和分解的影响,更高的温度可能导致生长速率降低。GaN 的 V/III 比率通常比砷化镓 (GaAs) 等其他 III/V 材料所使用的比率高得多 (> 500)。

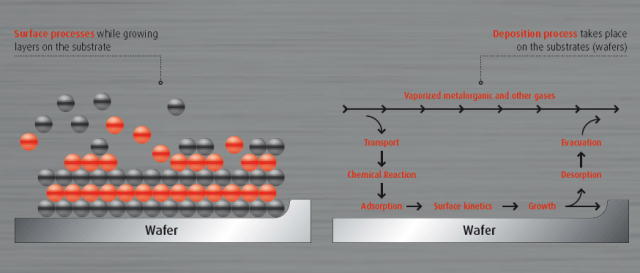

图 1 是 MOCVD 工艺的简化表示。

基材

蓝宝石(Al 2 O 3 )衬底通常用于GaN LED制造,具有相对便宜和光学透明的优点。碳化硅 (SiC) 具有比 Si 更好的晶格匹配和导热性的优点,但价格更昂贵。Si (111) 是功率 HEMT 应用中常用的衬底。

成核层 (NL)

NL 对于适应 GaN 和 Si 之间的大晶格失配 (~ 17%) 并为 GaN 生长提供二维表面至关重要。NL生长之前需要进行表面处理,例如喷涂一些Al或NH 3以形成粗糙的SiN x表面。这有助于减轻晶格失配引起的应力。NL 可以在 1,100 至 1,300 o C 的温度下生长,典型厚度约为 100 -200 nm。

缓冲层(BL)

GaN BL 需要具有高电阻,以防止直流泄漏和并联传导。未掺杂的 GaN 通常为 n 型,因此需要 p 型掺杂剂来解决这一问题。铁 (Fe) 和碳 (C) 是这种情况的候选者。通过调整沉积条件(例如流速、压力和温度),可以从 TMGa 源实现碳掺杂。并且具有不具有铁所具有的强烈记忆效应的优点。C 掺杂水平可以针对给定的击穿电压进行调节,大约需要 1e19 cm 3才能实现超过 700 V 的击穿电压。该缓冲层通常可以在 980 o C – 1,080 o C左右生长。

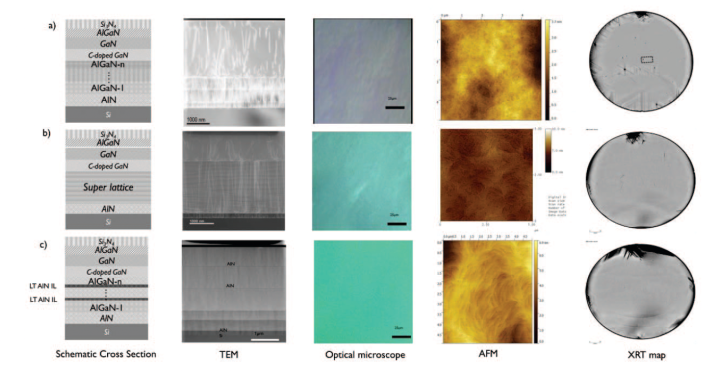

控制诸如螺纹缺陷 (TD) 等位错是 BL 的关键功能。已经尝试了多种方法,其中一些如图 2 所示。在图 2(a) 中,使用了阶梯式 AlGaN 缓冲层,Al 含量朝顶面逐渐减少。C含量的逐步掺杂也可以并行进行。AlN/(Al)GaN 的超晶格(SL)如图 2(b)所示,而 AlN 的低温中间层(IL)如图 2(c)所示。作者2表明,SL 和 IL 方法可以降低滑移线和裂纹的密度,从而允许使用更厚的净缓冲层来满足击穿电压要求,同时限度地减少晶圆弯曲。垂直传播的缺陷可以在 SL 或 IL 界面处终止。许多其他研究3已经证明,置于缓冲层中的约 10 nm AlN 的低温(LT:在约 600 o C 下生长)IL 可以减少应力并提高 GaN 沟道层的晶体质量。通常需要几微米的 BL 厚度。

阻隔层

AlGaN 势垒层的成分和厚度决定了器件的关键性能指标,例如阈值电压 (Vth) 和二维电子气 (2 DEG) 沟道密度和迁移率。Al 的百分比范围为 15 – 40%。在增强型 p-GaN HEMT 中,AlGaN 层通常可以为 10 -20 nm。高铝成分会导致形成欧姆接触变得困难,同时会提高沟道电荷密度。在沟道/势垒界面处使用薄的(约1 nm)AlN层用于创建势垒并防止2°G波函数穿透势垒。这也允许高铝成分势垒。另一个需要考虑的权衡是其厚度。为了提高 Vth,通常需要在栅极上设置薄势垒,以牺牲 2 DEG 电荷密度为代价。栅极区中的部分势垒凹槽,

选择性面积生长 (SAG)

MOCVD 的一个关键用途是在器件的选定区域中生长薄膜。可以使用诸如二氧化硅(SiO 2 )之类的掩模层来防止其他区域的生长。GaN HEMT 开发中 SAG 的一些示例包括:

欧姆接触区4的SAG :这里在器件的源极/漏极区中再生长n-GaN以降低源极电阻。

MISFET 和 MOSFET 等增强型 GaN 金属绝缘体半导体器件的关键挑战之一是栅极形成步骤中势垒层干法蚀刻造成的等离子体损伤。这会产生栅极泄漏和可靠性问题。[5] 中举例说明的一种解决方案是通过选择性地屏蔽栅极区域并使用 SAG 重新生长外延层来创建凹进式栅极GaN MOSFET。由于避免了蚀刻损坏,氧化铝 (Al 2 O 3 )/AlGaN/GaN MISFET 的性能得到了改善。

在 e 模式 p-GaN HEMT 中,沿着侧壁和靠近栅极的沟道访问区域的该层的蚀刻损坏会严重降低器件性能。栅极中掺镁 p-GaN 层的 SAG 是通过改进的栅极控制完成的 [6]。

高性能、高生产率的 MOCVD 工具现已配备内置工艺监控/控制自动晶圆处理和腔室清洁功能。Aixtron 的 G10-GaN Planetary Reactor?就是一个例子,它可以容纳 8×150 毫米或 5×200 毫米的晶圆。图 3 显示了在五个 200 mm 晶圆上实现的 AlGaN 势垒层的优异 Al 成分均匀性。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 交交型变频器和交直交型变频器的区别2025/9/29 10:53:22

- 800G DR8 与其他 800G 光模块的对比分析2025/9/29 10:30:18

- 接触器式继电器怎么区分 如何测量好坏2025/9/26 12:57:09

- 电容选型时如何选择产品的电压2025/9/18 15:01:07

- 电容器旁路的基本原理2025/9/17 15:33:46