模拟 IC 设计中的 MOSFET 非理想性

出处:维库电子市场网 发布于:2024-08-13 16:38:41

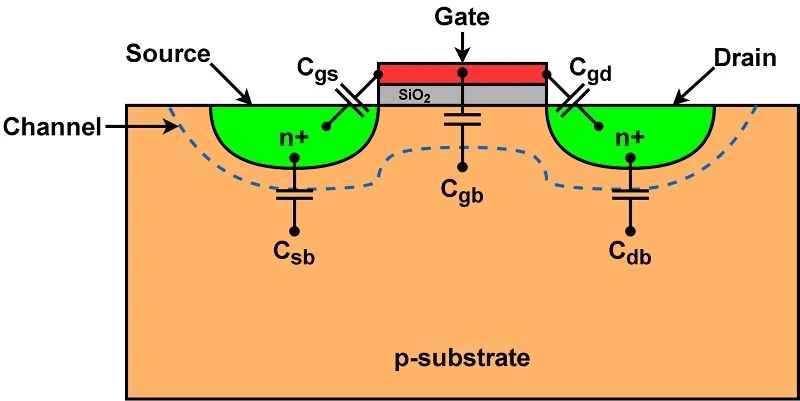

寄生电容

由于 MOSFET 的物理实现,在端子结之间形成了以下寄生电容:

C GS:栅极-源极电容。

C GD:栅极-漏极电容。

C GB:栅极至体电容。

C SB:源至体电容。

C DB:漏极至体电容。

在设计包含 MOSFET 的模拟 IC 时,这些电容对电路带宽影响很大。图 1 显示了它们的位置。

图 1.具有寄生电容的 MOSFET 结构。

电容值根据工作区域而变化,我们将在接下来的章节中讨论。

栅极-源极电容和栅极-漏极电容

虽然图 1 中没有显示,但在晶体管制造过程中,源极和漏极会略微延伸到栅极下方。在栅极与源极或漏极重叠的区域,会形成一个电容器,栅极氧化物 (SiO 2 ) 是它们之间的电介质。此重叠的长度称为L diff。

由氧化物电容 ( C ox )形成的栅极 - 源极 (或漏极) 电容的值可以按以下公式计算:

$$C_{GS}~=~C'_{ox}~\times~W~\times~L_{diff}$$等式 1.

在哪里:

C' ox等于 \(\frac{\epsilon_{ox}}{t_{ox}}\)ε ox是二氧化硅的介电常数

t ox是栅极氧化层的厚度(图1所示的高度)。

这个简单的栅极-源极(或漏极)电容公式仅在源极和漏极彼此分离时才有效,当晶体管处于截止或饱和状态时(因为通道会夹断)才有效。在线性区域中,源极和漏极通道实际上被电阻通道“短路”,因此我们只需要关注栅极和通道之间的氧化物电容。

由于该器件是对称的,因此在线性区域中,我们可以假设源极和漏极将各自占据氧化物电容值的一半。栅极 - 源极和栅极 - 漏极值可以计算如下:

$$C_{GS}~=~C_{GD}~=~\frac{1}{2}~\times~W~\times~L~\times~C'_{ox}$$等式 2.

栅极至体电容

C GD的值实际上由两个独立电容器的并联组合而成:

氧化电容,位于栅极和衬底之间。

耗尽电容器,形成于耗尽层(沟道和衬底之间的区域)与衬底之间。

氧化物电容值可利用以下公式计算:

$$C_{ox}~=~C'_{ox}~\times~W~\times~L$$

等式 3.

以及耗尽电容,使用这个:

$$C_{dep}~=~CGBO~\times~W~\times~L$$

等式 4.

其中CGBO是依赖于晶体管物理特性的栅极体重叠电容项。

氧化物和耗尽电容器彼此并联 - 当两者都存在时,它们相加。在截止区,由于栅极和主体之间没有通道,C GB 的值是公式 3 和公式 4 的总和。一旦存在通道,C ox就会与主体断开,就像我们之前讨论的栅极到源极/漏极电容一样。因此, C GD的值等于C dep,可以使用公式 4 找到。

源极至体电容和漏极至体电容

推导C SB和C DB的值需要大量的器件物理知识。这些值由结电容 ( C J ) 决定。C J的值由耗尽区宽度决定,而耗尽区宽度又取决于 MOSFET 内的掺杂浓度。

我们需要从中得出的结论是,C SB和C DB将保持在源极或漏极和主体之间的连接处恒定,因为端子的尺寸在操作区域之间不会改变。

电容值汇总

表 1 总结了 MOSFET 按工作区域的寄生电容值。

表 1.寄生电容值。

电容隔断线性 (Linear)饱和

C GS和C GD

\(C'_{ox}~\times~W~\times~L_{diff}\)

\( \frac{1}{2}~\times~W~\times~L~\times~C'_{ox}\)\(C'_{ox}~\times~W~\times~L_{diff}\)国标

\(C_{ox}~+~C_{dep}\)

\(C_ {dep} \)\(C_ {dep} \)

C SB和C DB

\(C_{J}\)

\(C_{J}\)\(C_{J}\)

身体效应

我们之前讨论了晶体管的体极和源极端子通常连接到相同的电位,但没有解释为什么会这样。为了理解原因,让我们更深入地了解一下当V GS的值从 0 增加到大于阈值电压 ( V th ) 时物理晶体管的情况。

随着V GS从零缓慢增加,硅中的正空穴被推离栅极,留下带负电的离子。这会产生耗尽层- 不存在电荷载流子的区域。随着V GS继续增加,栅极电荷开始慢慢增长到大于耗尽层的电荷,因此源极和漏极之间可以形成电子通道。

假设体电压变得比源极更负(V SB > 0)。现在更多的空穴被吸引到体端,导致在通道附近形成更大的耗尽区。这意味着阈值电压增加,因为现在需要更大的栅极电压来克服耗尽区的电荷并形成通道。当V SB < 0 时,情况相反:在通道附近形成较小的耗尽区,并且V th相应地下降。

MOSFET 中体效应的一个例子。

图 2. I D与V GS随V SB变化的关系(浅蓝色: V SB = 0 V;绿色: V SB = –0.5 V;红色: V SB = 0.5 V)。

关于体效应的阈值电压可以计算如下:

$$V_{th}~=~V_{th0}~+~\gamma \sqrt{2 \Phi_{F}~+~V_{SB}}~-~\sqrt{2| \Phi_{F}|}$$等式 5.

在哪里:

V th0是标称阈值电压

Φ F是硅的费米势。

体效应对模拟设计有很大的影响——将晶体管堆叠在一起是很常见的,这会导致体效应以非平凡的方式改变阈值电压。

通道长度调制

理论上,饱和状态下的晶体管应充当具有无限输出电阻的完美电流源。实际上,当沟道夹断时,V DS仍会对漏极电流产生影响,因此晶体管的输出电阻很大但有限。这是由于一种称为沟道长度调制的现象,其中随着饱和区漏极电压的增加,沟道长度开始逐渐减小。

为了适应沟道长度调制,我们将饱和状态下的漏极电流方程调整为:

$$I_{D}~=~\mu C_{ox} \frac{W}{L}( V_{GS}~-~V_{th})^{2} ( 1~+~ \lambda V_{DS} )$$等式 6.

通道长度调制系数λ 计算如下:

$$\frac{\Delta L}{L} V_{DS}~=~\lambda$$

等式 7.

由此,我们可以计算出饱和状态下的输出电阻(ROUT)为:

$$R_{OUT}~=~\frac{1}{ \mu \lambda C_{ox} \frac{W}{L} ( V_{GS}~-~V_{th})^{2} }$$等式 8.

亚阈值传导

之前,我们定义了三个晶体管工作区域:截止、线性和饱和。实际上,还有第四个:亚阈值区域,这在超低功耗模拟 IC 设计中非常流行。

形成该区域的原因是,晶体管不会在V GS低于V th时准确关闭。相反,扩散电流在源极和漏极之间形成一个小通道。当V GS < V th时,该扩散电流不可忽略,并且与V GS呈指数相关。由此产生的亚阈值区域的I - V曲线计算如下:

$$I_{D}~=~I_{S}e^{(\frac{V_{GS}}{ \xi V_{T}})}$$等式 9.

在哪里:

I S是晶体管的特定电流,与 \frac{W}{L}\) 成正比。

ξ 是非理想因子(在硅中 > 1)

V T是热电压,等于\(\frac{k\text{T}}{q}\)。

迁移率下降和速度饱和

晶体管内的漂移电流由内部电场决定,随着晶体管尺寸的缩小,其电场迅速增加。事实证明,对于短沟道晶体管,晶体管内可以实现的少数载流子速度有一个值。这被称为饱和速度。

这限制了某些器件相对于V GS和V DS 的电流增加,因为它们的驱动电流终会达到值。此外,随着电场的不断增加,这些载流子的迁移率会降低,导致在这些非常高的电压下驱动电流会降低。这种短沟道效应是现代晶体管行为的众多方面之一,无法通过我们在上一篇文章中研究的平方律方程来预测。

漏极诱导势垒降低 (DIBL)

当V DS变得足够大时,漏极开始吸引负电荷到栅极下方的表面,帮助栅极形成通道。因此,有效阈值电压会降低,形成V th与V DS成反比的关系。这被称为漏极感应势垒降低,简称 DIBL。

上一篇:硬件模拟的基本原理

下一篇:什么是脉冲频率调制?

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 运算放大器压摆率的核心要点2025/9/5 16:27:55

- 深度剖析放大器稳定系数 K 与 Mu 的差异2025/9/2 16:44:05

- 什么是运算放大器失调电流2025/9/1 17:01:22

- 什么是运算放大器电源电压抑制比(PSRR)2025/9/1 16:48:49

- 有没有适配m1的模拟器2025/8/11 16:55:19