模拟设计中的布局相关和 LOD 效应

出处:维库电子市场网 发布于:2024-11-12 17:09:17

随着工艺几何尺寸的减小,引入了一种新型的可变性,统称为“布局相关效应”,简称 LDE。

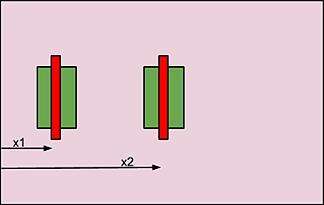

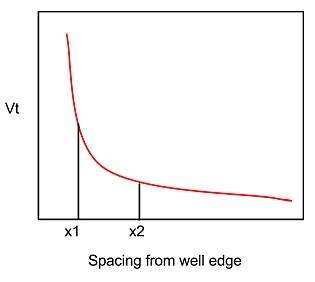

LDE 的一个例子是设备靠近井边缘。器件到阱边缘的距离对器件的Vt(阈值电压)有影响。原因是注入离子从用于限定阱的抗蚀剂侧壁散射,从而使Vt增加了几毫伏,甚至几十毫伏。 (参见“深度纳米级 CMOS 中的布局相关邻近效应”,John V Faricelli,IEEE CICC 2010。)

图1

图2

扩散效应长度

Vt 的变化不仅会引起失配效应,还会引起显着的性能变化。其他影响可能是由于硅中无意的应力,例如由器件之间的浅沟槽隔离引起的。这种应力会影响器件中的载流子迁移率,从而影响电流。这称为“扩散长度”或 LOD 效应,其中器件的特性根据其栅极与扩散边缘的距离而变化。

要使用 LDE 效果进行设计,可以使用各种布局技术:

使用相似的扩散尺寸、形状、方向

设备与井缘之间的距离较大

添加虚拟设备和/或虚拟多晶硅以使指状设备更加平等

然而,设计的仿真需要早期布局以及寄生提取,以便能够在仿真过程中对 LDE 效应进行建模。所有这些都打破了现有的定制设计流程,传统上,电路设计师将初步原理图(可能使用估计的寄生参数进行模拟)交给布局工程师,然后布局工程师创建初始布局以提取真实的寄生参数。然后将其交回电路设计以优化器件参数以满足性能目标,并且通常需要多次布局/优化迭代。

下一篇:风模拟器简介

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 信号发生器的专业使用方法详解2025/4/22 17:16:58

- TI - 德州仪器模拟设计 | 运算放大器基本稳定性概述2025/4/9 16:10:57

- 使用模拟预测进行RF功率放大器线性化2025/4/7 16:13:43

- 了解电动机模拟器的特征2025/3/31 16:43:29

- 控制系统中模拟信号的示例2025/3/26 17:20:13