DC-DC BUCK转换器设计技巧和技巧

出处:网络整理 发布于:2025-03-12 17:15:18

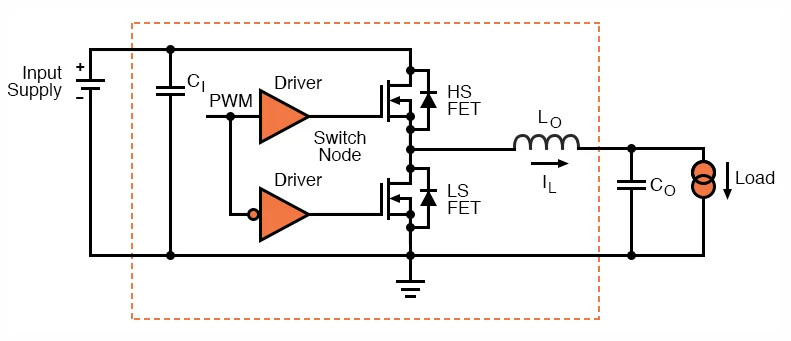

在开始之前,让我们回顾一下DC-DC Buck Converter的电路:

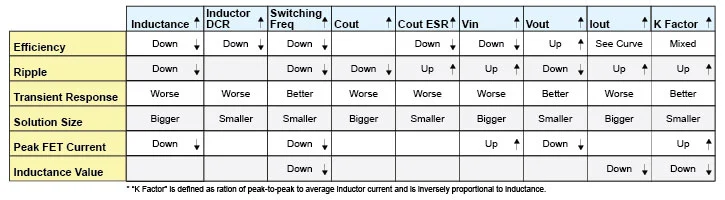

了解您面临的设计权衡很重要。

为了帮助您,我在Buck Design中开发了一个“影响什么”的矩阵:

主要的权衡是选择电感(与k因子,即峰值与峰值与平均电感器电流的比率相反),输出电容和开关频率以实现足够的纹波和瞬态响应。

设计人员应该利用调节器IC制造商的设计工具来确定组件值和电路模拟。

了解您的电容器

确保电容器在操作频率下具有电容,并知道其自动频率在哪里。

陶瓷在广泛的频率上很好,但电容相对较低。通常,一种电容器类型不能覆盖整个频率范围,并且必须并行使用两种类型(例如,陶瓷和电解性),陶瓷靠近电路。

电容器还通过施加的偏置电压损失了很多额定电容。

信任但验证:芯片和组件

在由第三方制造的具有微小且未标记的组件的PCB上,您必须相信板填充器安装了正确的组件。确保您的信任不会放错。

如果您已将芯片发送到制造商进行故障分析,请不要等待结果。如今,芯片质量水平很高,芯片极不可能使您不好。该分析也需要一些时间。同时,您可能会发现真正的问题。

如果您使用的是数字芯片,请验证您已更改的设置实际上已写入芯片中,而不仅仅是GUI。

考虑测试和测量

不要假设直流电压在不使用范围验证的情况下是稳定的。

测量涟漪的过程很多 - 执行它的合适设备很昂贵。虽然使用精美的差分探针,但您可以使用单端探测器 - 仅确保接地线非常短,并且在V OUT旁边连接。

使用1倍探针(您可以自己构建)。 10倍探针将没有您需要的灵敏度。

通过电感器的寄生电容,HF尖峰夫妇升至输出。您可能需要减慢上部MOSFET的转机,以减少底部MOSFET的振铃或DV/DT伪造的转盘,尽管这会降低效率。

分析您的输入电容

输入电容比输出电容少得多,但是要达到输入噪声要求并确保电路不会饿死电路。

输入电容器具有较大的波纹电流,在50%占空比的峰值上达到峰值,产生热量并缩短帽子的寿命。确保电流属于其规格。当您添加更多的平行c时,会有一个基本的权衡,因为较低的ESR会导致更高的波纹电流和更多的加热。为了真正使输入纹波电流下降,您可能需要一个系列电感器。

由于占空比较高,因此C的当前绘制较高,从而导致芯片下的d下垂的v越多,如果您已经接近越来越接近较低的V in limimimimen,则这将变得很重要-在这些情况下,您可能需要添加C。

提前考虑PCB布局

了解当前路径的基础知识和高电流环的化。学校教了很多有关前进电路路径的知识,但对回程道路一无所知,这显示为完美的地面符号!进行布局,以使返回电流可以遵循其自然路径(化的循环)。

保持功率路径电感较低。通过它们脉动电流会产生电压尖峰和辐射EMI。高功率vias还可以,但应理解它们的特征。

了解电路节点的阻抗水平并相应地保护它们。例如,误差放大器的求和节点是高阻抗,并且对噪声敏感 - 将其隔离并使其小。

尊重模拟,数字和电源之间的分区,并提供自然的回程路径。恒星接地避免通过与敏感,低级电路共享的地面路径进行大型脉动电流。

上一篇:在高压服务器电源中使用低压设备

下一篇:ADC采集电压误差较大的解决策略

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 电源设计故障防护:现代保护 IC 的简单解决方案2025/8/5 16:10:25

- 电源噪声的来源与应对策略2025/8/4 16:31:13

- 直流可编程电源串联或并联连接的优势2025/8/4 16:25:37

- 解析 BUCK 电路:负载电流增大时电感纹波电流的变化2025/7/31 15:59:18

- 深度解析 DC-DC 电源 PCB 设计关键要点2025/7/30 16:50:03