逻辑电平测量器电路原理

出处:lsx32 发布于:2011-09-01 08:16:37 | 1746 次阅读

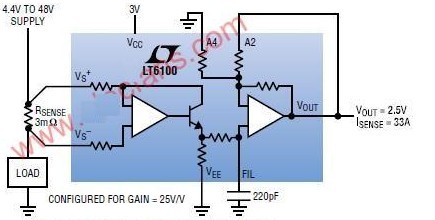

该电路可用来检测电平变化频率不太高的逻辑电平,对于TTL电平、CMOS电平均可检测。

电路如图所示,7555用作滞后电平比较器。当探头P接触高电平时,7555输出低电平使LED1亮、LED2暗。当P接触低电平时,7555输出高电平使LED1不亮,LED2亮。

用来测TTL电平时,电源可采用4.5V电池供电,调W使7555第5脚电压为2.4V.这时2.4V以上为高电平,1.2V以下为低电平。

用于测量CMOS电平时,电源电压需与被测逻辑电路电源电压相近,W中心头断开不用。这时高于电源电压三分之二为高电平,低于电源电压三分之一为低电平。

在测量时还会遇到眼睛来不及观察判断逻辑电平高低的情形,这可根据LED1与LED2不同的发光强度来估计脉冲占空比是大于50%还是小于50%.占空比是大于50%则LED1较亮,反之则LED2较亮。

上一篇:电缆故障测试仪电路原理

下一篇:低成本高灵敏度电压表电路设计

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。