何时校准系统失调电压和增益误差

出处:维库电子市场网 发布于:2024-10-28 15:54:17 | 403 次阅读

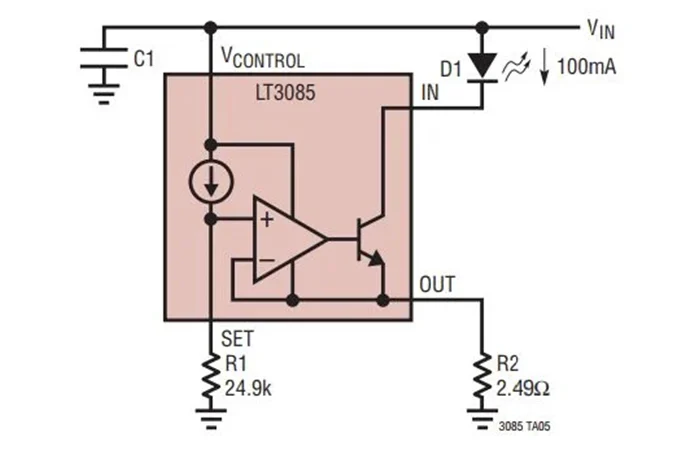

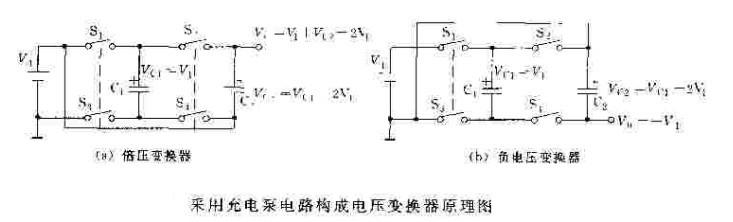

图 1显示了增益为 100 V/V、输入信号为 45 mV 且 V OS为 1 mV 的运算放大器。偏移信号直接添加到输入信号中,从而引入 2.22% 的误差。您可以通过选择具有更好失调规格的运算放大器或通过实施校准程序来减少此误差。

何时校准系统失调电压和增益误差

校准将两个不同的校准信号施加到运算放大器并测量其响应。然后,您可以使用测量结果对传递函数进行直线曲线拟合,并使用数学模型来校正运算放大器的增益和失调误差。这种方法甚至适用于包含多个运算放大器和模数转换器 (ADC) 的复杂模拟系统。

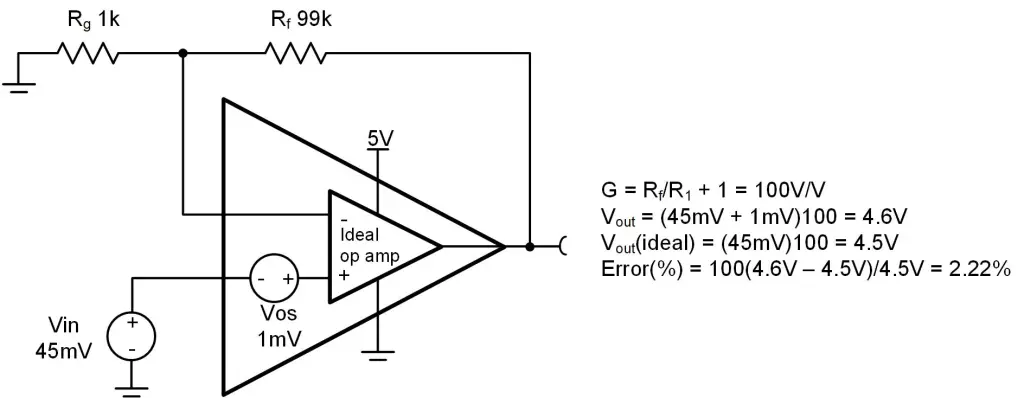

图 2和方程式 1、2、3 和 4 显示了使用失配 0.1% 的电阻器的简单两点校准示例。除了校正失调之外,该方法还可以校正由电阻器容差引起的增益误差。

何时校准系统失调电压和增益误差

方程 1显示了校准线性系统时使用的一般直线方程。公式 2和公式 3显示了增益和失调校准系数的计算。请注意,增益的理想值为 2.0 V/V,但由于电阻容差,测量结果为 2.00088 V/V。

何时校准系统失调电压和增益误差

此外,理想的偏移为 0 V,但偏移计算结果为 31.25 μV。公式 4显示了如何使用校准系数来校正增益和失调误差,以确定更准确的 V IN值。

如上例所示,运算放大器增益误差主要是由用于设置放大器增益的电阻容差引起的 (G = Rf/Rg +1)。 0.1% 的容差适用于标称室温值,因此,单次校准可以最大限度地减少室温增益误差。然而,如果不添加额外的温度校准步骤,就不可能校准增益误差漂移(或随温度变化的增益误差变化)。

增益误差漂移是由反馈电阻温度系数不匹配引起的。因此,电阻分压器网络可以最大限度地减少增益误差漂移,因为内部电阻的温度系数匹配。

以RES11A电阻分压器网络为例,其最大增益误差为±0.05%,最大增益漂移误差为±2 ppm/°C。在许多情况下,使用具有此精度级别的电阻器可以消除校准的需要,从而降低测试复杂性。

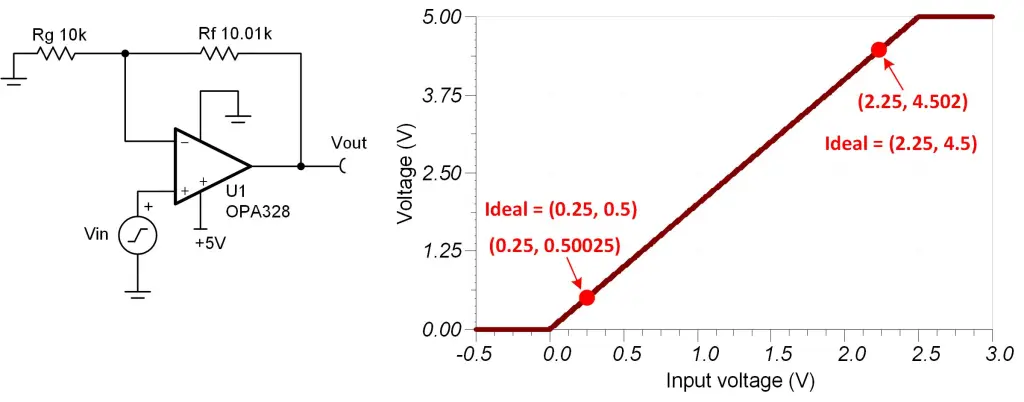

偏移校准过程的局限性之一是有许多系统变量会影响 V OS的值。在校准中考虑这些次要影响通常很困难或不可能。例如,温度变化会影响V OS。

从技术上讲,您可以监控温度并纠正电源电压的变化,但从实际角度来看,这样做会使校准过程变得复杂且昂贵。共模输入电压、电源电压和开环增益都会产生额外的输入失调电压。

这些参数在运算放大器数据表中指定,以便您可以通过计算和仿真来估计预期误差的范围。

您可以在运算放大器选择过程中选择高性能器件,以最大限度地减少这些错误。例如,OPA189 的典型共模抑制比 (CMRR) 为 168 dB。这种非常高的 CMRR 意味着共模中 1V 的变化将导致偏移量发生 4nV 的变化。因此,对于该器件,改变共模信号对 V OS 的影响实际上可以忽略不计。

某些误差源可能会产生运算放大器数据表中未指定的额外偏移,因为它们可归因于 PCB 设计或外部环境因素。例如,在 PCB 上施加机械应力可能会导致运算放大器输入失调电压发生变化。环境因素产生额外偏移电压的另一个例子是寄生热电偶。

这些寄生热电偶是由反馈网络、输入连接和 PCB 走线中使用的不同金属引起的,当 PCB 具有显着的热梯度或应用非常敏感时,这主要是一个问题。在具有中等热梯度的环境中,热电动势(EMF)将在微伏范围内。

何时校准系统失调电压和增益误差

校准还是不校准?

校准既是技术也是财务的设计决策。如果您的模拟系统需要自动最终测试验证,校准可以允许使用精度较低的组件,但仍能实现良好的精度。

在不需要自动最终测试的情况下,添加校准可能成本高昂,更好的方法是使用精密运算放大器和电阻网络来减少总体误差。

精密元件还有一个额外的好处,即可以最大限度地减少 CMRR、PSRR、A OL和温度漂移等次要误差源。这些次要误差源很难通过校准来消除。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。