作者:林世霖,华清远见嵌入式学院深圳中心讲师。类型转换是C语言中常识性的知识点,但不注意又会有让人迷惑的时候,来看一道笔试题:以下两个程序片段A和B,问那个for循环能运行?A:------------------------------...

分类:EDA/PLD/PLC 时间:2010-01-27 阅读:6084 关键词:C语言类型转换C语言

作者:高倩,谢海良 漯河职业技术学院 近年来,随着生活水平的不断改善,个人财富日益增长,人们对安全防盗的要求也逐渐提高。安全可靠、使用方便的电子密码锁成了人们...

分类:EDA/PLD/PLC 时间:2010-01-25 阅读:4450 关键词:基于Max+PlUsⅡ和VHDL的电子密码锁设计EPLK30QC208-2Max+PlUsⅡVHDL

赛灵思高性能40nm Virtex-6 FPGA系列通过验证

赛灵思公司(Xilinx, Inc.)与半导体代工厂商联华电子( UMC)共同宣布,采用联华电子高性能40nm工艺的Virtex-6 FPGA,已经完全通过生产前的验证。这是双方工程团队为进一步...

分类:EDA/PLD/PLC 时间:2010-01-22 阅读:3622 关键词:赛灵思高性能40nm Virtex-6 FPGA系列通过验证FPGA

作者:潘闻融,周智 电子科技大学 0引言 当今社会,芯片技术与人们的生活密切相关,在各种电子产品中都有芯片的身影,而且,它们往往是电子产品关键的技术。制造芯片的流程非常复杂而且资源投入巨大,保证芯片...

分类:EDA/PLD/PLC 时间:2010-01-20 阅读:3288 关键词:基于C++TCL PLI联合仿真下的芯片验证方法研究C++TCL 芯片

随着FPGA密度的增加,系统设计人员能够开发规模更大、更复杂的设计,从而将密度优势发挥到。这些大规模设计基于这样的设计需求——需要在无线通道卡或者线路卡等现有应用中加入新功能,或者通过把两种芯片功能合并到...

分类:EDA/PLD/PLC 时间:2010-01-13 阅读:2093 关键词:借助物理综合提高FPGA设计效能FPGA

1 引 言 由于雷达所处的环境的复杂性,除了地物、云雨、鸟群等干扰外,还可能来自临近的雷达异步干扰、电台干扰等。所有的干扰,经过接收机进入信号处理机,虽然经过了中频信号的处理,但还可能有残余。因此,为...

分类:EDA/PLD/PLC 时间:2010-01-12 阅读:2469 关键词:雷达视频积累算法在FPGA上的实现XC18V01AD9432XC3S1000FPGA

摘 要 介绍了采用FPGA和DSP直接控制硬盘进行数据存储的方法,并采用一片FIFO作为数据缓存,能够满足80Khz数据采样率系统的存盘要求。 1 引言 数据存储是数据采集过程中的一个重要环节,目前大部分数据存储...

分类:EDA/PLD/PLC 时间:2010-01-11 阅读:2964 关键词:采用FPGA和DSP直接控制硬盘实现存储控制的方法72V2101FPGADSP

利用基于SystemC/TLM的方法学进行IP开发和FPGA建模

随着系统级芯片技术的出现,设计规模正变得越来越大,因而变得非常复杂,同时上市时间也变得更加苛刻。通常RTL已经不足以担当这一新的角色。上述这些因素正驱使设计师开发新的方法学,用于复杂IP(硬件和软件)以及复...

分类:EDA/PLD/PLC 时间:2010-01-08 阅读:2685 关键词:利用基于SystemC/TLM的方法学进行IP开发和FPGA建模FPGA

引 言 门和人类文明是孪生的,它伴随着人类文明的发展而跃动。21 世纪的今天,门更加突出了安全理念,强调了有效性:有效地防范、通行、疏散,同时还突出了建筑艺术的理念,强调门与建筑以及周围环境整体的协调、...

分类:EDA/PLD/PLC 时间:2010-01-08 阅读:2905 关键词:基于EDA 技术(FPGA)的自动门控制系统设计MC33033EDAFPGA控制系统

1.引言指针是C/C++语言的特色,而数组名与指针有太多的相似,甚至很多时候,数组名可以作为指针使用。于是乎,很多程序设计者就被搞糊涂了。而许多的大学老师,他们在C语言的教学过程中也错误得给学生讲解:“数组名...

分类:EDA/PLD/PLC 时间:2010-01-06 阅读:2489 关键词:C/C++数组名与指针区别深层探索C/C++

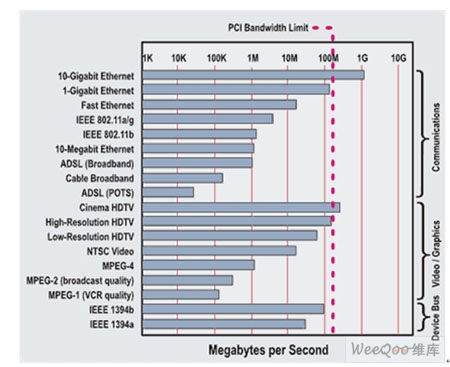

采用中档FPGA设计面向PCI Express系统的解决方案

基于ISA(工业标准架构)总线的扩展卡最初在1978年问世,由于要求提升系统整体性能,MCA(微通道架构)等总线系统或是扩展的ISA总线随后也相继出现。鉴于数据通道宽度(主要是8...

分类:EDA/PLD/PLC 时间:2010-01-05 阅读:2900 关键词:采用中档FPGA设计面向PCI Express系统的解决方案FPGAPCIExpress系统

Xilinx®SystemGeneratoRForDSP是用来协助系统设计的MATLABSimulink模块集。SystemGeneratorforDSP在熟悉的MATLAB环境中引入XilinxFPGA对象,让您能够对设计进行功能仿真,并且使用MATLAB环境对照理想参考结果验...

分类:EDA/PLD/PLC 时间:2010-01-05 阅读:2771 关键词:HDL设计和验证与System Generator相结合HDL

高度复杂的SoC设计正面临着高可靠性、高质量、低成本以及更短的产品上市周期等日益严峻的挑战。可测性设计通过提高电路的可测试性,从而保证芯片的高质量生产和制造。借助于EDA技术,可以实现可测试性设计的自动化,...

分类:EDA/PLD/PLC 时间:2010-01-04 阅读:3178 关键词:利用EDA工具提高系统级芯片测试的效率EDA|芯片

C语言的编译链接过程要把我们编写的一个c程序(源代码)转换成可以在硬件上运行的程序(可执行代码),需要进行编译和链接。编译就是把文本形式源代码翻译为机器语言形式的目标文件的过程。链接是把目标文件、操作系...

分类:EDA/PLD/PLC 时间:2009-12-31 阅读:14767 关键词:C语言编译过程总结详解C语言

摘要:本文简要分析结构体、联合体2种特殊的数据类型,结合链表和结构体的综合运用,详细注释创建链表的计算机执行和处理的过程,并对一些概念结合代码举例分析,指出常见错误和问题。结构体结构体是一种特殊的数据...

分类:EDA/PLD/PLC 时间:2009-12-31 阅读:8555 关键词:C语言中结构体与联合体的简单用法C语言

C语言中的“结构体”其实就相当于其他高级语言中的“记录”,结构体的定义方法如下:例如:Structstudent{intnum;charname[20];charsex;intage;floatscore;charaddr[30];};(注意最后的

分类:EDA/PLD/PLC 时间:2009-12-31 阅读:57817 关键词:C语言结构体定义C语言

函数名:fgets功能:从流中读取一个字符串用法:char*fgets(char*string,intn,FILE*stream);形参注释:*string:结果数据的首地址;n-1:一次读入数据块的长度,其默认值为1k,即1024;stream文

分类:EDA/PLD/PLC 时间:2009-12-31 阅读:3516 关键词:标准I/O库函数:fgets与gets比较分析

约瑟夫问题:N个人围成一圈,从第M个位置开始按1.2.3...报数报到K的就出圈,请问出圈的人的顺序.请用链表实现该功能。约瑟夫问题可以用循环单链表解决,循环单链表的特点是链表中最后一个节点的指针域不再是NULL,而是...

分类:EDA/PLD/PLC 时间:2009-12-31 阅读:8871 关键词:约瑟夫问题C语言代码实现过程C语言

引言:对于指针,正确的分配动态内存是十分重要的,本文将着重阐述动态内存分配函数malloc,calloc,realloc以及memset的用法。 一、对于malloc,在终端输入 #:man malloc可以知道函数原型是: Void *calloc(siz...

分类:EDA/PLD/PLC 时间:2009-12-31 阅读:12446 关键词:C语言动态内存分配函数解析C语言

供应商、企业以及服务提供商认为100G系统最终会在市场上得到真正实施。推动其实施的主要力量是用户持续不断的宽带需求。各种标准组织正在制定传送网和以太网以及光接口100G标准。对于希望在标准发布之前,先期设计10...

分类:EDA/PLD/PLC 时间:2009-12-30 阅读:2925 关键词:采用FPGA实现100G光传送网FPGA