引言 液晶显示已成为目前平板电视与计算机显示终端的主流,液晶显示器的研究设计、生产、检验等部门甚至消费者需要用一些定量或定性的方法和指标去检验液晶显示器的质量...

分类:通信与网络 时间:2020-07-10 阅读:1020 关键词:基于FPGA和VHDL语言编程实现液晶屏信号发生器的设计FPGA,信号发生器

目前,信号处理技术、通信技术和多媒体技术的迅猛发展都得益于DSP[3]技术的广泛应用。但是对于便携式和家用的语音系统而言,基于一般的DSP芯片的设计方案并不理想。首先DSP的芯片成本以及开发成本在现阶段仍然是比较...

时间:2019-01-08 阅读:971 关键词:基于FPGA与VHDL语言实现音频处理芯片设计与仿真分析芯片

摘要:本文提出了一种基于VHDL语言的数字频率计的设计方案,该方案通过采用自顶向下的设计方法,用VHDL语言对状态机、计数器、十分频、同步整形电路等进行编程,用Quartus...

分类:电子测量 时间:2013-12-09 阅读:3770 关键词:基于VHDL语言的数字频率计的设计方案VHDL数字频率计测量仪器

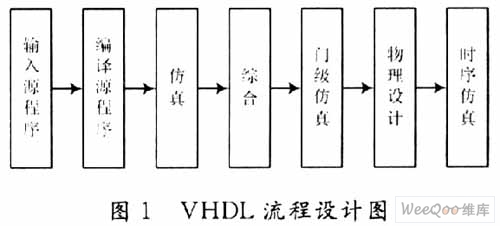

0 引言 VHDL超高速集成电路硬件描述语言是随着集成电路系统化和高度集成化逐步发展起来的,是一种用于数字系统设计、测试,面向多领域、多层次的IEEE标准硬件描述语言。...

分类:EDA/PLD/PLC 时间:2010-06-03 阅读:3476 关键词:VHDL语言为核心的EDA技术在医学中的应用VHDL语言

0 引 言 VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起来的。它是一种面向设计、多层次的硬件描述语言,是集...

分类:EDA/PLD/PLC 时间:2010-03-19 阅读:3862 关键词:基于CPLD/FPGA的VHDL语言电路优化设计EPM7192CPLDFPGAVHDL

按键开关是电子设备实现人机对话的重要器件之一。由于大部分按键是机械触点,在触点闭合和断开时都会产生抖动。为避免抖动引起误动作造成系统的不稳定,就要求消除按键的抖动,确保按键每按只做响应。随着可编程逻辑...

分类:EDA/PLD/PLC 时间:2009-12-30 阅读:5092 关键词:基于VHDL语言的按键消抖电路设计及仿真VHDL语言

引言代码纯化.指在代码设计中及完成后进行自定义的、IEEE标准的、设计重用的、可综合性和可测试性等方面的规则检查;代码覆盖率分析.研究仿真中的测试矢量是否足够;设计性能和面积分析.在设计逻辑综合过程中分析...

分类:EDA/PLD/PLC 时间:2009-01-13 阅读:2703 关键词:基于VHDL语言的IP核验证设计XC2S150TEST3VHDL语言IP

摘 要:介绍了VHDL语言及其基本特点,讨论了VHDL语言在EDA中的诸多优点,并以交通信号灯主控制电路的设计为例,说明了用VHDL语言设计数字电路的方法以及VHDL语言在数字电路设计仿真中的重要作用,给出了交通信号灯...

分类:EDA/PLD/PLC 时间:2007-11-24 阅读:3260 关键词:VHDL语言在EDA仿真中的应用

摘 要:伪随机序列发生器是序列密码设计中的重要环节,FCSR是其中一类重要思想。本文介绍了FCSR的特性和产生方法,并用VHDL语言予以实现,给出FCSR序列的主程序和仿真波形,指出需要注意的问题。 关键词:进位移...

分类:EDA/PLD/PLC 时间:2007-11-24 阅读:2731 关键词:FCSR原理及其VHDL语言的实现

引言在IC(integratedcircuit.集成电路)发展到超大规模阶段的今天,基于IP(IntellectualProperty,知识产权)核的IC设计及其再利用是保证SoC(systemonchip,片上系统)开发效率和质量的重要手段。如果

分类:EDA/PLD/PLC 时间:2007-06-14 阅读:1985 关键词:基于VHDL语言的IP核验证XC2S150

在数字通信网中,为了扩大传输容量,提高信道利用率,常常需要把若干个低速数字信号合并成一个高速数字信号,然后通过高速信道传输,数字复接就是实现这种数字信号合并的专门技术。数字复接把低速数字信号合并为高速...

分类:EDA/PLD/PLC 时间:2007-05-27 阅读:2230 关键词:一种用VHDL语言实现的帧同步算法

摘要:通过一个偶同位产生器逻辑功能的实现过程,介绍了VHDL语言中信号设置的不同方 式及注意事项,并给出了完整的程序代码。关键词:VHDL;程序中图分类号:TP312 文献标识码:A 文章编号:1003-353X(2002)03-0045-...

分类:EDA/PLD/PLC 时间:2007-05-25 阅读:3245 关键词:VHDL语言中信号设置的不同方式及注意事项20021979XINLINX

VHDL语言在PSpice中的仿真应用张涛(华南理工大学电子与信息学院广东广州510641)随着科学技术的快速发展,电路仿真技术的应用达到了一个新的阶段。作为EDA工具的PSpice是能对模拟信号和数字信号进行仿真分析的非常好...

前言 随着EDA技术得发展,CPLD已经在许多方面得到了广泛应用,而串行通信是实现远程测控的重要手段。本文利用VHDL语言在CPLD上实现了串行通信,完全可以脱离单片机使用,克服了单片机的许多缺点。 串口结构及内容...

分类:EDA/PLD/PLC 时间:2007-04-16 阅读:1750 关键词:用VHDL语言在CPLD上实现串行通信(图)

摘 要:卷积码是一种性能优良的差错控制编码。本文在阐述卷积 码编解码器基本工作原理的基础上,提出了在MAX+PlusⅡ开发平台上基于VHDL语言设计 (2,1,6)卷 积码编解码器的方法。仿真实验结果表明了该编解码器的...

分类:通信与网络 时间:2007-04-10 阅读:2371 关键词:基于VHDL语言的卷积码编解码器的设计

在定时电路中,合适而准确的时钟脉冲基准信号极其重要,一般用晶振作为基准信号。但晶体产品因制造的不一致性,或者恶劣的环境干扰(如高温高压等),会带来晶振时基有别,如果电路设计中没有加以考虑,同类电路产品之...

分类:其它 时间:2006-06-24 阅读:215 关键词:基于VHDL语言的定时时基校正电路设计ICL7106CPL