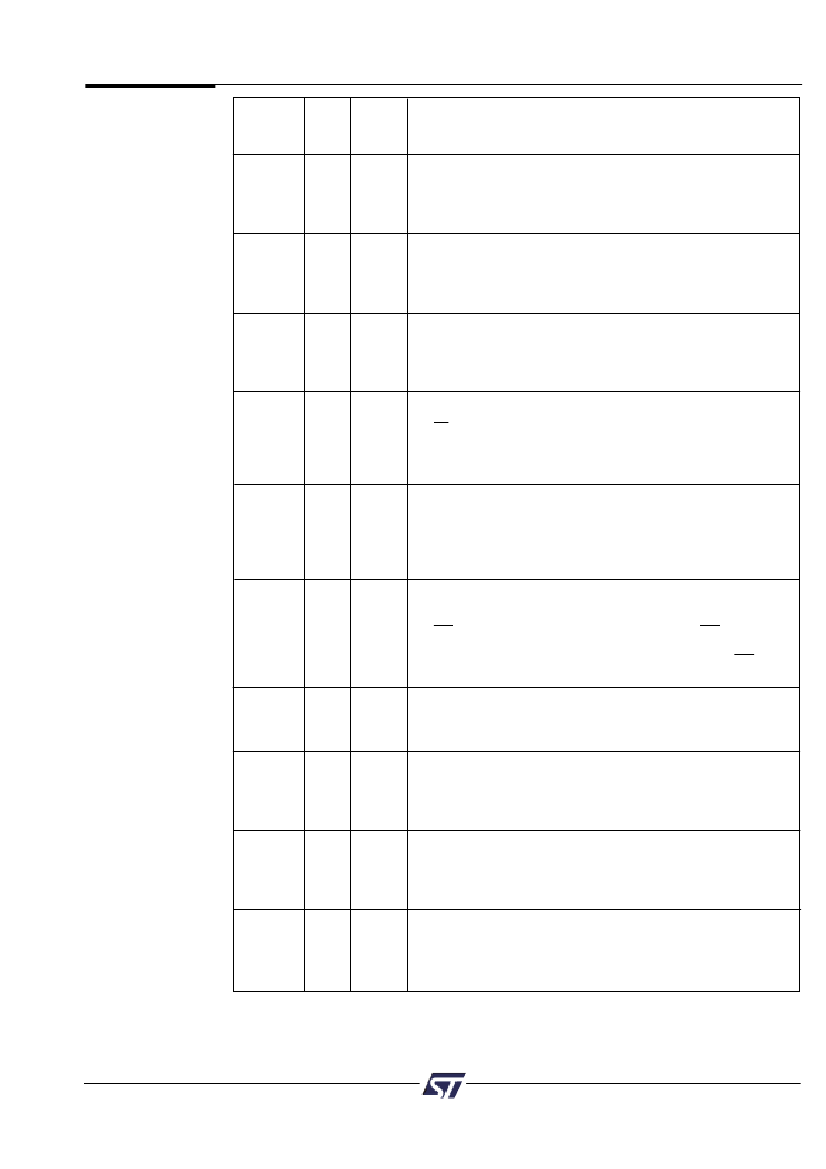

PSD835G2

PSD8XX Family

Pin*

(TQFP

Pin Name Pkg.)

PA0-PA7 51-58

Table 5.

PSD835G2

Pin

Descriptions

(cont.)

Type

I/O

CMOS

or Open

Drain

I/O

CMOS

or Open

Drain

I/O

CMOS

or Slew

Rate

I/O

CMOS

or Open

Drain

Description

Port A, PA0-7. This port is pin configurable and has multiple

functions:

1. MCU I/O 鈥?standard output or input port

2. CPLD Micro鈬擟ell (MCell A0-7) output.

3. Latched, transparent or registered PLD input.

Port B, PB0-7. This port is pin configurable and has multiple

functions:

1. MCU I/O 鈥?standard output or input port.

2. CPLD Micro鈬擟ell (MCell B0-7) output.

3. Latched, transparent or registered PLD input.

Port C, PC0-7. This port is pin configurable and has multiple

functions:

1. MCU I/O 鈥?standard output or input port.

2. External chip select (ECS0-7) output.

3. Latched, transparent or registered PLD input.

Port D pin PD0 can be configured as:

1. ALE or AS input 鈥?latches addresses on ADIO0-15 pins

2. AS input 鈥?latches addresses on ADIO0-15 pins on the

rising edge.

3. Input to the PLD.

4. Transparent PLD input.

Port D pin PD1 can be configured as:

1. MCU I/O

2. Input to the PLD.

3. CLKIN clock input 鈥?clock input to the CPLD

Micro鈬擟ells, the APD power down counter and CPLD

AND Array.

Port D pin PD2 can be configured as:

1. MCU I/O

2. Input to the PLD.

3. CSI input 鈥?chip select input. When low, the CSI enables

the internal PSD memories and I/O. When high, the

internal memories are disabled to conserve power. CSI

trailing edge can get the part out of power-down mode.

Port D pin PD3 can be configured as:

1. MCU I/O

2. Input to the PLD.

Port E, PE0. This port is pin configurable and has multiple

functions:

1. MCU I/O 鈥?standard output or input port.

2. Latched address output.

3. TMS input for JTAG/ISP interface.

Port E, PE1. This port is pin configurable and has multiple

functions:

1. MCU I/O 鈥?standard output or input port.

2. Latched address output.

3. TCK input for JTAG/ISP interface (Schmidt Trigger).

Port E, PE2. This port is pin configurable and has multiple

functions:

1. MCU I/O 鈥?standard output or input port.

2. Latched address output.

3. TDI input for JTAG/ISP interface.

PB0-PB7 61-68

PC0-PC7 41-48

PD0

79

PD1

80

I/O

CMOS

or Open

Drain

PD2

1

I/O

CMOS

or Open

Drain

PD3

2

I/O

CMOS

or Open

Drain

I/O

CMOS

or Open

Drain

I/O

CMOS

or Open

Drain

I/O

CMOS

or Open

Drain

PE0

71

PE1

72

PE2

73

9