PSD8XX Family

PSD835G2

PSD8XX

Architectural

Overview

(cont.)

4.5 ISP via JTAG Port

In-System Programming can be performed through the JTAG pins on Port E. This serial

interface allows complete programming of the entire PSD835G2 device. A blank device

can be completely programmed. The JTAG signals (TMS, TCK, TSTAT, TERR, TDI, TDO)

can be multiplexed with other functions on Port E. Table 3 indicates the JTAG signals pin

assignments.

4.6 In-System Programming (ISP)

Using the JTAG signals on Port E, the entire PSD835G2 (memory, logic, configuration)

device can be programmed or erased without the use of the microcontroller.

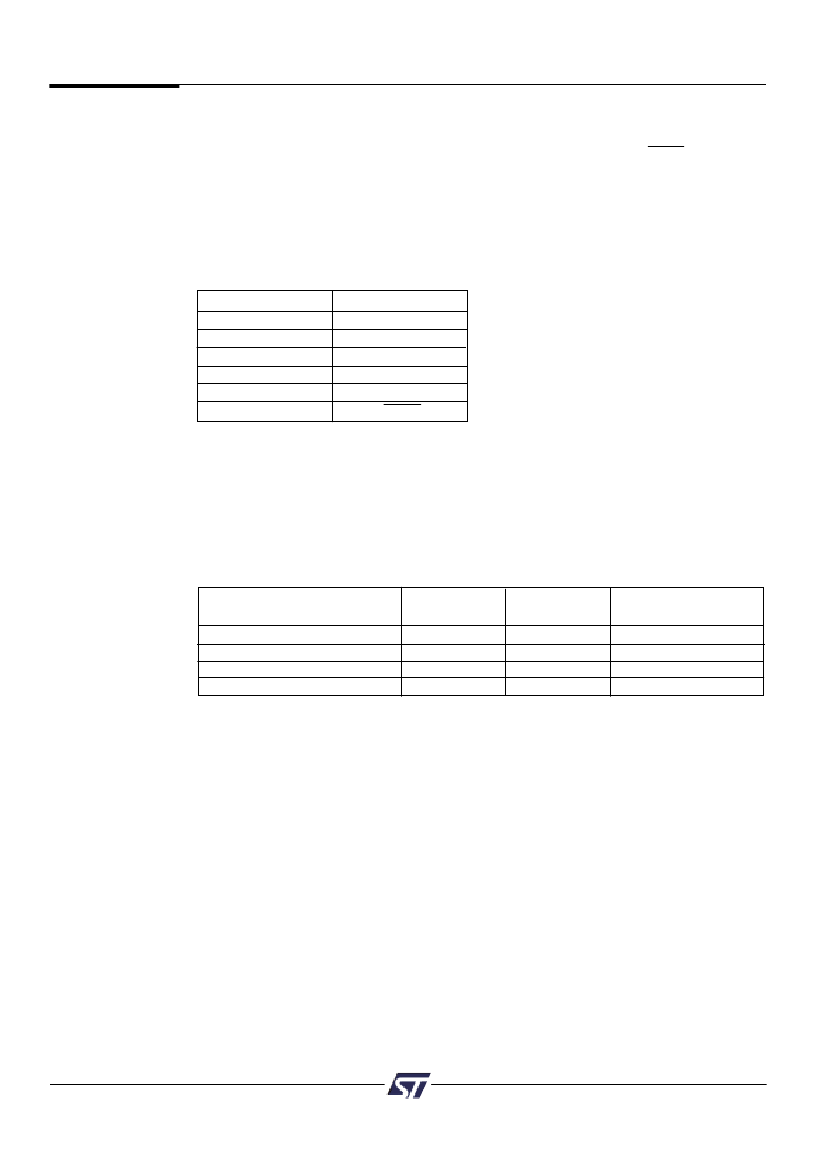

Table 3. JTAG Signals on Port E

Port E Pins

PE0

PE1

PE2

PE3

PE4

PE5

JTAG Signal

TMS

TCK

TDI

TDO

TSTAT

TERR

4.7 In-Application re-Programming (IAP)

The main Flash memory can also be programmed in-system by the microcontroller

executing the programming algorithms out of the secondary Flash memory, or SRAM.

Since this is a sizable separate block, the application can also continue to operate. The

secondary Flash boot memory can be programmed the same way by executing out of the

main Flash memory. Table 4 indicates which programming methods can program different

functional blocks of the PSD8XX.

Table 4. Methods of Programming Different Functional Blocks of the PSD835G2

Functional Block

Main Flash memory

Flash Boot memory

PLD Array (DPLD and CPLD)

PSD Configuration

JTAG-ISP

Yes

Yes

Yes

Yes

Device

Programmer

Yes

Yes

Yes

Yes

IAP

Yes

Yes

No

No

4.8 Page Register

The eight-bit Page Register expands the address range of the microcontroller by up to

256 times.The paged address can be used as part of the address space to access

external memory and peripherals or internal memory and I/O. The Page Register can also

be used to change the address mapping of blocks of Flash memory into different memory

spaces for IAP.

4.9 Power Management Unit

The Power Management Unit (PMU) in the PSD835G2 gives the user control of the

power consumption on selected functional blocks based on system requirements. The

PMU includes an Automatic Power Down unit (APD) that will turn off device functions due

to microcontroller inactivity. The APD unit has a Power Down Mode that helps reduce

power consumption.

The PSD835G2 also has some bits that are configured at run-time by the MCU to reduce

power consumption of the CPLD. The turbo bit in the PMMR0 register can be turned off

and the CPLD will latch its outputs and go to standby until the next transition on its inputs.

Additionally, bits in the PMMR2 register can be set by the MCU to block signals from

entering the CPLD to reduce power consumption. See section 9.5.

6