HYB25D256[16/40/80]0C[E/C/F/T](L)

256 Mbit Double-Data-Rate SDRAM

Functional Description

3.2.3

Read Latency

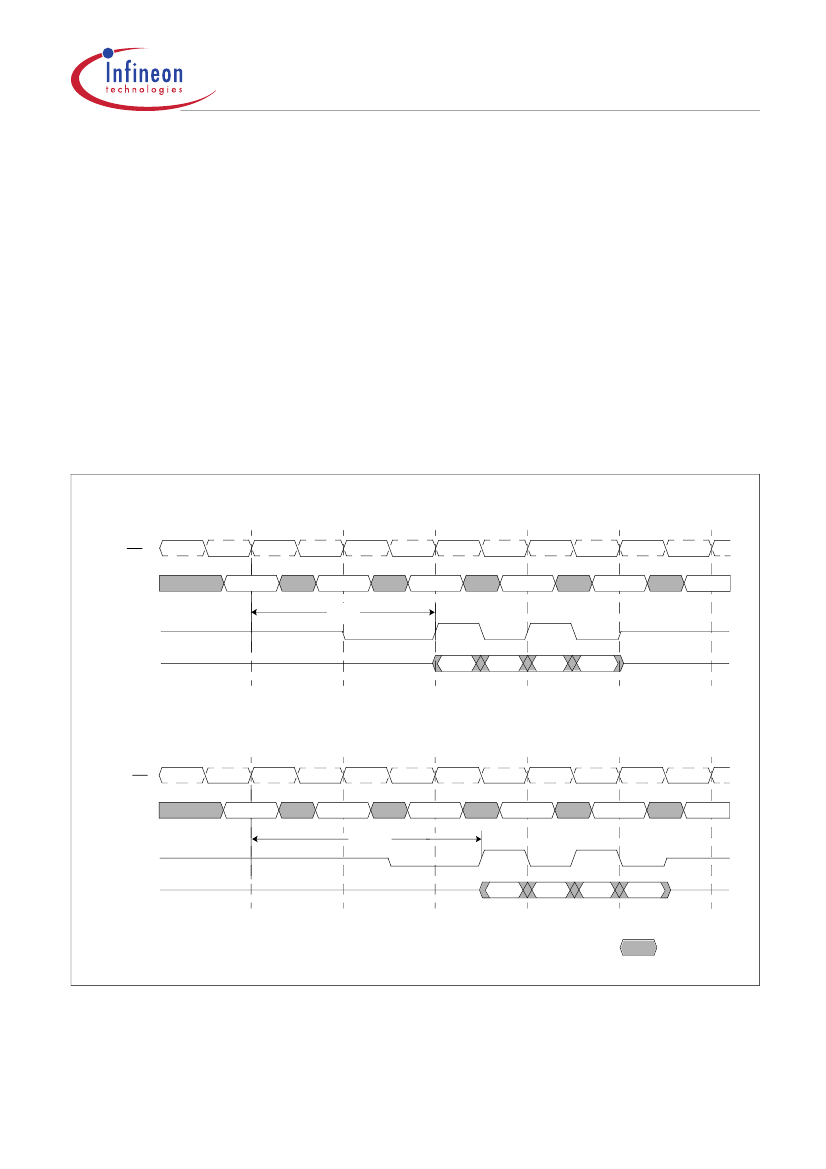

The Read latency, or CAS latency, is the delay, in clock cycles, between the registration of a Read command and

the availability of the first burst of output data. The latency can be programmed 2, 2.5 and 3 clocks. CAS latency

of 1.5 is supported for DDR200 components only.

If a Read command is registered at clock edge n, and the latency is

m

clocks, the data is available nominally

coincident with clock edge

n + m

(see

Figure 6).

Reserved states should not be used as unknown operation or incompatibility with future versions may result.

3.2.4

Operating Mode

The normal operating mode is selected by issuing a Mode Register Set Command with bits A7-A12 set to zero,

and bits A0-A6 set to the desired values. A DLL reset is initiated by issuing a Mode Register Set command with

bits A7 and A9-A12 each set to zero, bit A8 set to one, and bits A0-A6 set to the desired values. A Mode Register

Set command issued to reset the DLL should always be followed by a Mode Register Set command to select

normal operating mode.

All other combinations of values for A7-A12 are reserved for future use and/or test modes. Test modes and

reserved states should not be used as unknown operation or incompatibility with future versions may result.

CAS Latency = 2, BL = 4

CK

CK

Command

Read

NOP

CL=2

DQS

DQ

NOP

NOP

NOP

NOP

CAS Latency = 2.5, BL = 4

CK

CK

Command

Read

NOP

CL=2.5

DQS

DQ

NOP

NOP

NOP

NOP

Shown with nominal t

AC

, t

DQSCK

, and t

DQSQ

.

Don鈥檛 Care

Figure 6

Required CAS Latencies

Data Sheet

25

Rev. 1.6, 2004-12