HYB25D256[16/40/80]0C[E/C/F/T](L)

256 Mbit Double-Data-Rate SDRAM

Functional Description

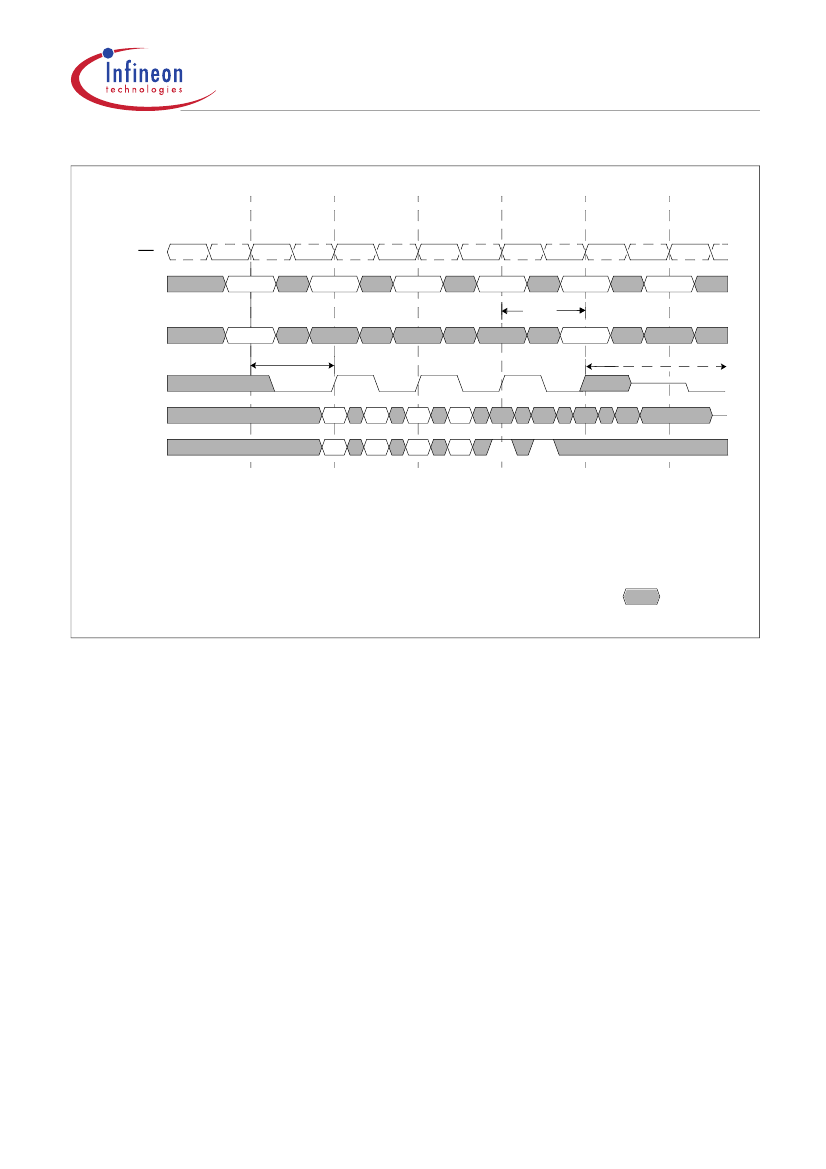

T1

CK

CK

Command

Write

T2

T3

T4

T5

T6

NOP

NOP

NOP

Read

NOP

t

WTR

Address

BAa, COL b

BAa, COL n

t

DQSS

(nom)

DQS

DQ

DM

DI a-b

CL = 2

1

1

DI a-b = data in for bank a, column b.

An interrupted burst is shown, 4 data elements are written.

3 subsequent elements of data in are applied in the programmed order following DI a-b.

t

WTR

is referenced from the first positive CK edge after the last desired data in pair.

The Read command masks the last 2 data elements in the burst.

A10 is Low with the Write command (Auto Precharge is disabled).

The Read and Write commands are not necessarily to the same bank.

1 = These bits are incorrectly written into the memory array if DM is low.

Don鈥檛 Care

Figure 25

Write to Read: Nominal DQSS, Interrupting (CAS Latency = 2; Burst Length = 8)

Data Sheet

50

Rev. 1.6, 2004-12