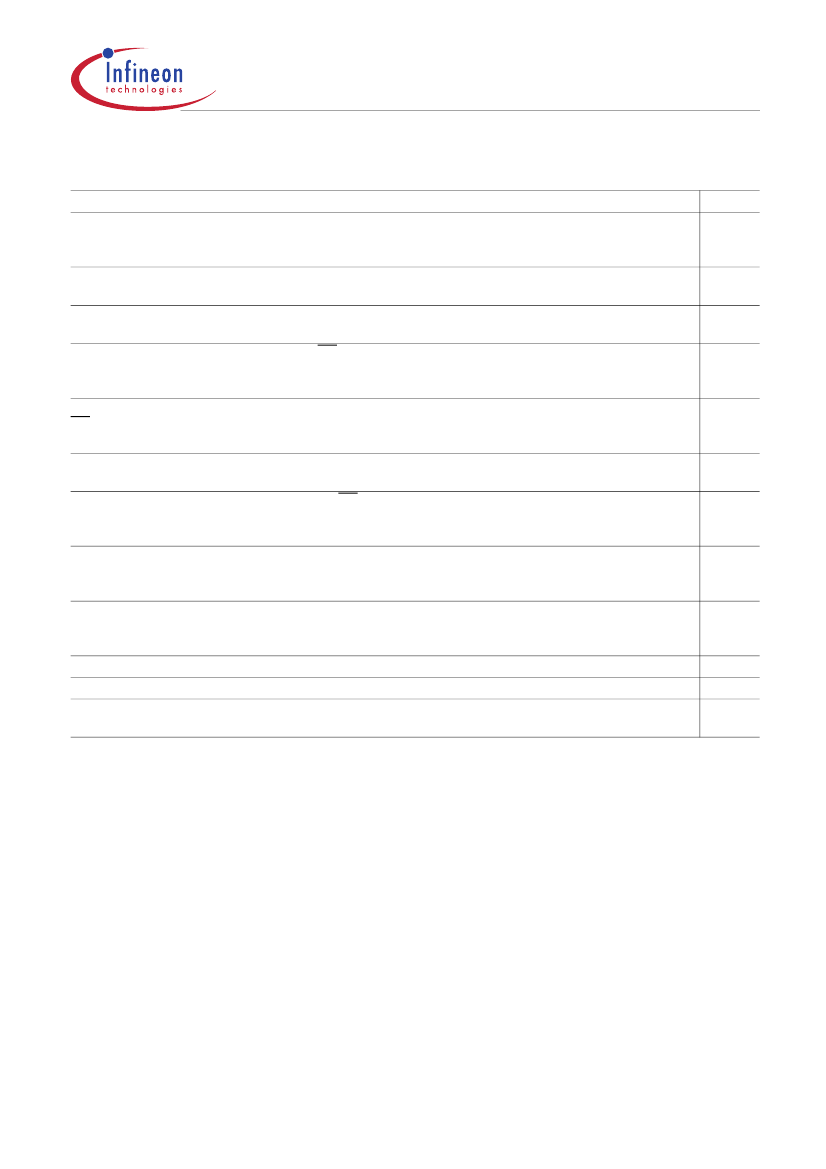

鈮?/div>

V

IHMIN

;

t

RC

=

t

RASMAX

;

t

CK

=

t

CKMIN

;

I

DD3N

DQ, DM and DQS inputs changing twice per clock cycle; address and control inputs changing once per

clock cycle.

Operating Current:

one bank active; Burst = 2; reads; continuous burst; address and control inputs

I

DD4R

changing once per clock cycle; 50% of data outputs changing on every clock edge; CL = 2 for DDR200

and DDR266A, CL = 3 for DDR333;

t

CK

=

t

CKMIN

;

I

OUT

= 0 mA

Operating Current:

one bank active; Burst = 2; writes; continuous burst; address and control inputs

I

DD4W

changing once per clock cycle; 50% of data outputs changing on every clock edge; CL = 2 for DDR200

and DDR266A, CL = 3 for DDR333;

t

CK

=

t

CKMIN

Auto-Refresh Current:

t

RC

=

t

RFCMIN

, burst refresh

Self-Refresh Current:

CKE

鈮?/div>

0.2 V; external clock on;

t

CK

=

t

CKMIN

Operating Current:

four bank; four bank interleaving with BL = 4; Refer to the following page for

detailed test conditions.

I

DD5

I

DD6

I

DD7

Data Sheet

74

Rev. 1.6, 2004-12