5.10

t

CH

t

CK

t

CL

t

RP

t

WR

Figure 48

Data Sheet

t

IH

VALID

NOP

NOP

NOP

NOP

PRE

NOP

NOP

ACT

t

IH

RA

t

IH

CK

CK

t

IH

t

IS

CKE

t

IH

t

IS

Command

NOP

Write

t

IS

A0-A9, A11, A12

COL n

t

IS

ALL BANKS

RA

A10

ONE BANK

t

IH

DIS AP

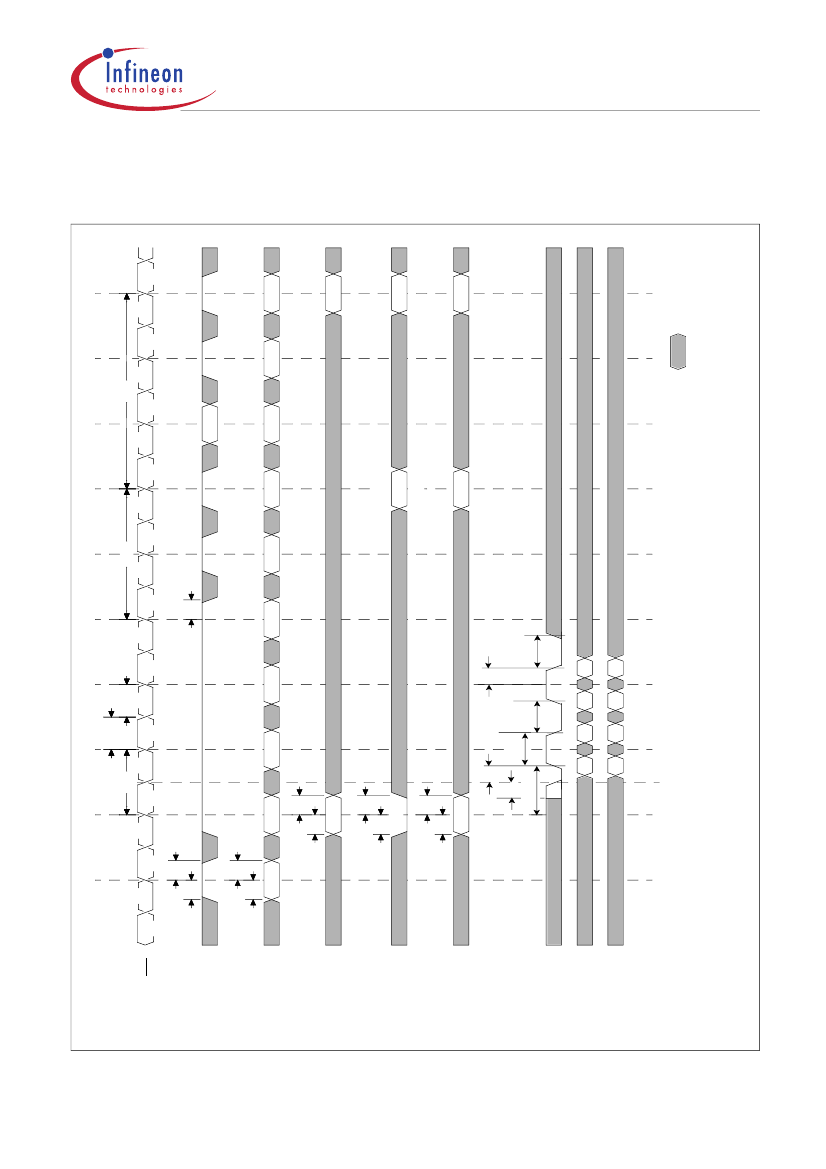

Write: Without Auto Precharge Command

Figure 48

shows the timing diagram for Write without Auto Precharge.

Write without Auto Precharge (Burst Length = 4)

86

BA x

BA x*

t

WPRE

t

DQSH

t

DQSS

t

WPST

t

DQSL

t

DSH

DIn

t

IS

BA

BA0, BA1

t

WPRES

DQS

DQ

DM

HYB25D256[16/40/80]0C[E/C/F/T](L)

256 Mbit Double-Data-Rate SDRAM

Timing Diagrams

Rev. 1.6, 2004-12

t

DQSS

= min.

DIn = Data in for column n.

3 subsequent elements of data in are applied in the programmed order following DIn.

DIS AP = Disable Auto Precharge.

*

= Don't care if A10 is High at this point.

PRE = Precharge; ACT = Active; RA = Row address; BA = Bank address.

NOP commands are shown for ease of illustration; other valid commands may be possible at these times.

Don鈥檛 Care