鈥?/div>

Overview

Features

Double data rate architecture: two data transfers per clock cycle

Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the

receiver

DQS is edge-aligned with data for reads and is center-aligned with data for writes

Differential clock inputs (CK and CK)

Four internal banks for concurrent operation

Data mask (DM) for write data

DLL aligns DQ and DQS transitions with CK transitions

Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

Burst Lengths: 2, 4, or 8

CAS Latency: 1.5 (DDR200 only), 2, 2.5, 3

Auto Precharge option for each burst access

Auto Refresh and Self Refresh Modes

RAS-lockout supported

t

RAP

=

t

RCD

7.8

碌s

Maximum Average Periodic Refresh Interval

2.5 V (SSTL_2 compatible) I/O

V

DDQ

= 2.5 V

卤

0.2 V (DDR200, DDR266, DDR333);

V

DDQ

= 2.6 V

卤

0.1 V (DDR400)

V

DD

= 2.5 V

卤

0.2 V (DDR200, DDR266, DDR333);

V

DD

= 2.6 V

卤

0.1 V (DDR400)

P-TFBGA-60-12 package with 3 depopulated rows (8

脳

12 mm

2

)

P-TSOPII-66 package

Lead- and halogene-free = green product

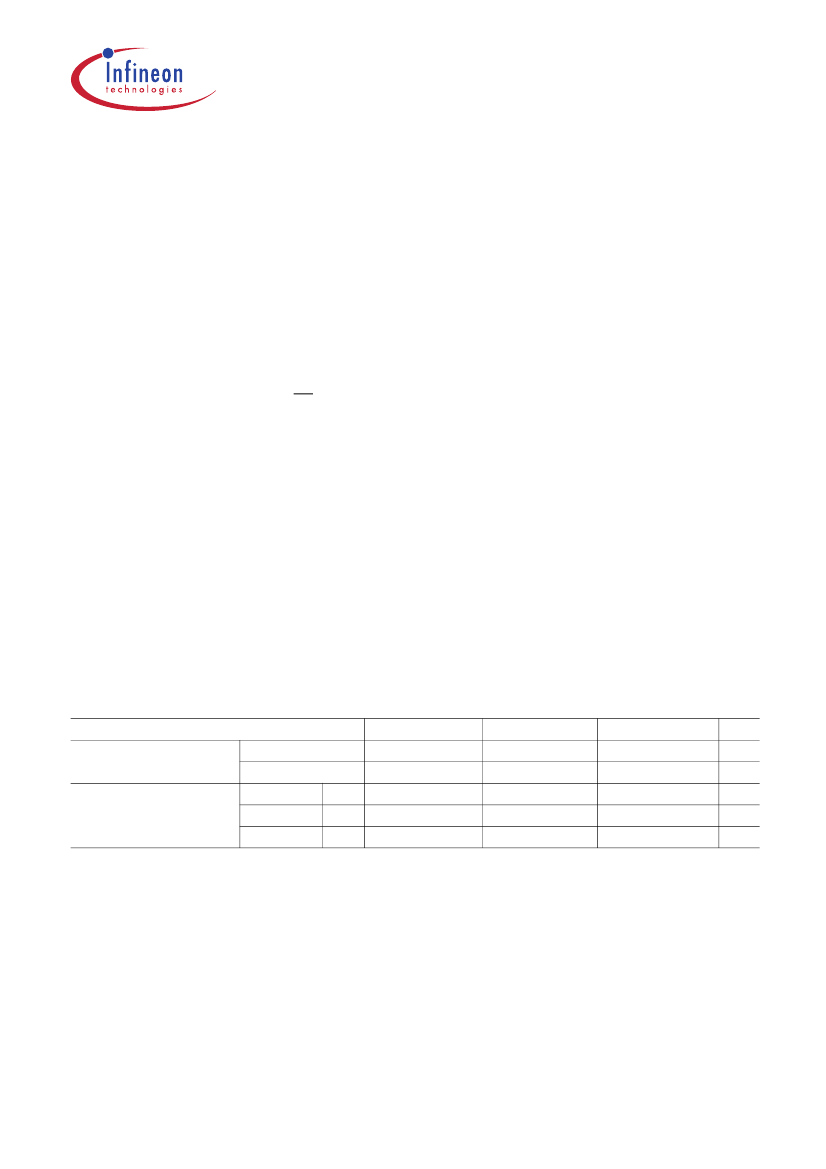

Performance

鈥?

Component

Module

@CL3

@CL2.5

@CL2

DDR400B

PC3200-3033

鈥?

DDR333

PC2700鈥?533

166

166

133

鈥?

DDR266A

PC2100-2033

鈥?/div>

143

133

Unit

鈥?/div>

鈥?/div>

MHz

MHz

MHz

Table 1

Part Number Speed Code

Speed Grade

max. Clock Frequency

f

CK3

200

f

CK2.5

166

f

CK2

133

Data Sheet

9

Rev. 1.6, 2004-12