鈮?/div>

4.5 V.

V

l

nA INPUT

GND

t PHL

V OH

nY OUTPUT

V OL

VM

t PLH

VM

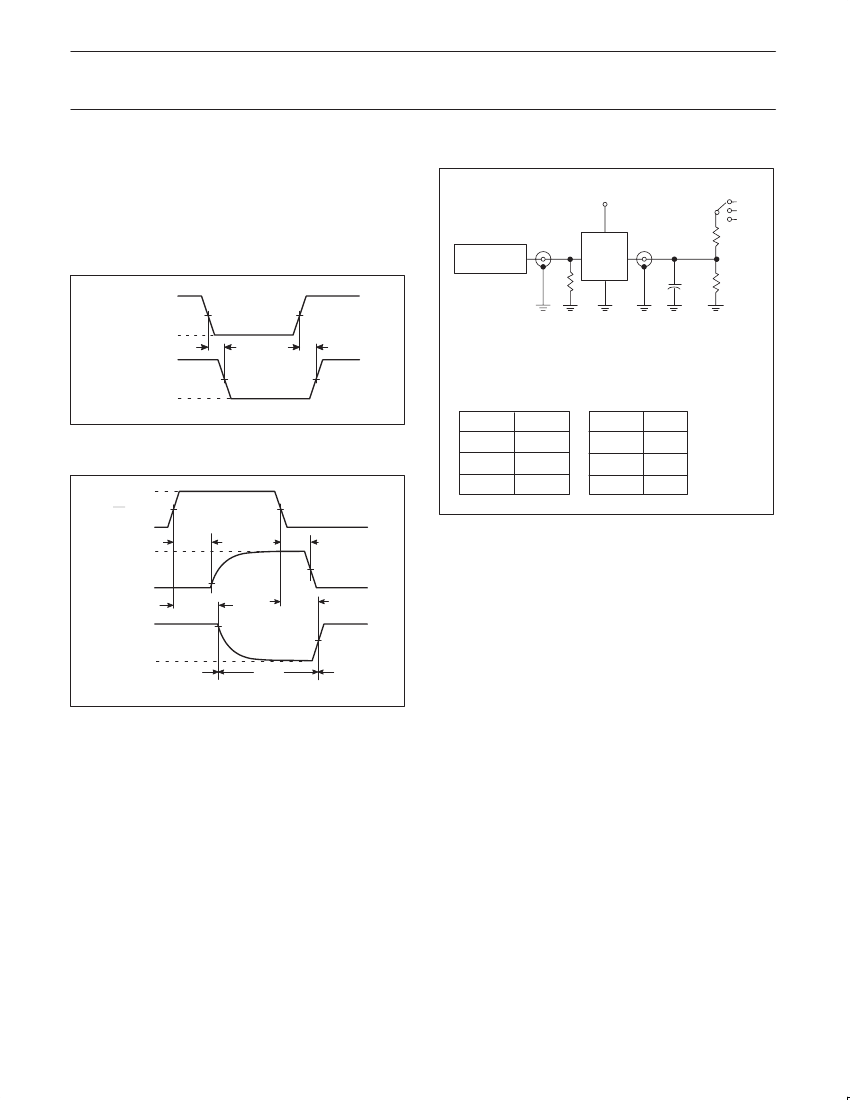

TEST CIRCUIT

V

CC

2 * V

CC

Open

GND

V

O

D.U.T.

R

T

C

L

50 pF

R

L

= 1k

R

L

= 1k

V

I

PULSE

GENERATOR

Test Circuit for Outputs

DEFINITIONS

R

L

= Load resistor

C

L

= Load capacitance includes jig and probe capacitiance.

R

T

= Termination resistance should be equal to Z

OUT

of pulse generators.

SWITCH POSITION

SV00459

TEST

t

PLH/

t

PHL

t

PLZ/

t

PZL

S

1

Open

2 * V

CC

GND

V

CC

< 2.7V

2.7鈥?.6V

w

4.5V

V

I

V

CC

2.7V

V

CC

Figure 1. Input (nA) to output (nY) propagation delays

and output transition times.

VI

nOE Input

GND

tPLZ

VCC

OUTPUT

LOW-to-OFF

OFF-to-LOW

VOL

tPHZ

VOH

OUTPUT

HIGH-to-OFF

OFF-to-HIGH

GND

outputs

enabled

VY

VM

outputs

disabled

outputs

enabled

tPZL

VM

VX

tPZH

VM

t

PHZ/

t

PZH

SV00896

Figure 3. Load circuitry for switching times.

SV00458

Figure 2. 3-state enable and disable times.

1998 Apr 28

6