93C66A/B

3.0

FUNCTIONAL DESCRIPTION

3.2

Data In (DI) and Data Out (DO)

Instructions, addresses, and write data are clocked into

the DI pin on the rising edge of the clock (CLK). The DO

pin is normally held in a HIGH-Z state except when

reading data from the device, or when checking the

READY/BUSY status during a programming operation.

The READY/BUSY status can be veri铿乪d during an

ERASE/WRITE operation by polling the DO pin; DO

low indicates that programming is still in progress, while

DO high indicates the device is ready. The DO will enter

the HIGH-Z state on the falling edge of the CS.

It is possible to connect the Data In (DI) and Data

Out (DI) pins together. However, with this con铿乬uration

it is possible for a 鈥渂us con铿俰ct鈥?to occur during the

鈥渄ummy zero鈥?that precedes the READ operation, if A0

is a logic-high level. Under such a condition the voltage

level seen at DO is unde铿乶ed and will depend upon the

relative impedances of DO and the signal source driv-

ing A0. The higher the current sourcing capability of A0,

the higher the voltage at the DO pin.

3.1

START Condition

3.3

Data Protection

The START bit is detected by the device if CS and DI

are both high with respect to the positive edge of CLK

for the 铿乺st time.

Before a START condition is detected, CS, CLK, and DI

may change in any combination (except to that of a

START condition), without resulting in any device oper-

ation (ERASE, ERAL, EWDS, EWEN, READ, WRITE,

and WRAL). As soon as CS is high, the device is no

longer in the standby mode.

An instruction following a START condition will only be

executed if the required amount of opcodes,

addresses, and data bits for any particular instruction is

clocked in.

After execution of an instruction (i.e., clock in or out of

the last required address or data bit) CLK and DI

become don't care bits until a new START condition is

detected.

During power-up, all programming modes of operation

are inhibited until V

CC

has reached a level greater than

3.8V. During power-down, the source data protection

circuitry acts to inhibit all programming modes when

Vcc has fallen below 3.8V at nominal conditions.

The ERASE/WRITE Disable (EWDS) and ERASE/

WRITE Enable (EWEN) commands give additional pro-

tection against accidentally programming during nor-

mal operation.

After power-up, the device is automatically in the

EWDS mode. Therefore, an EWEN instruction must be

performed before any ERASE or WRITE instruction

can be executed.

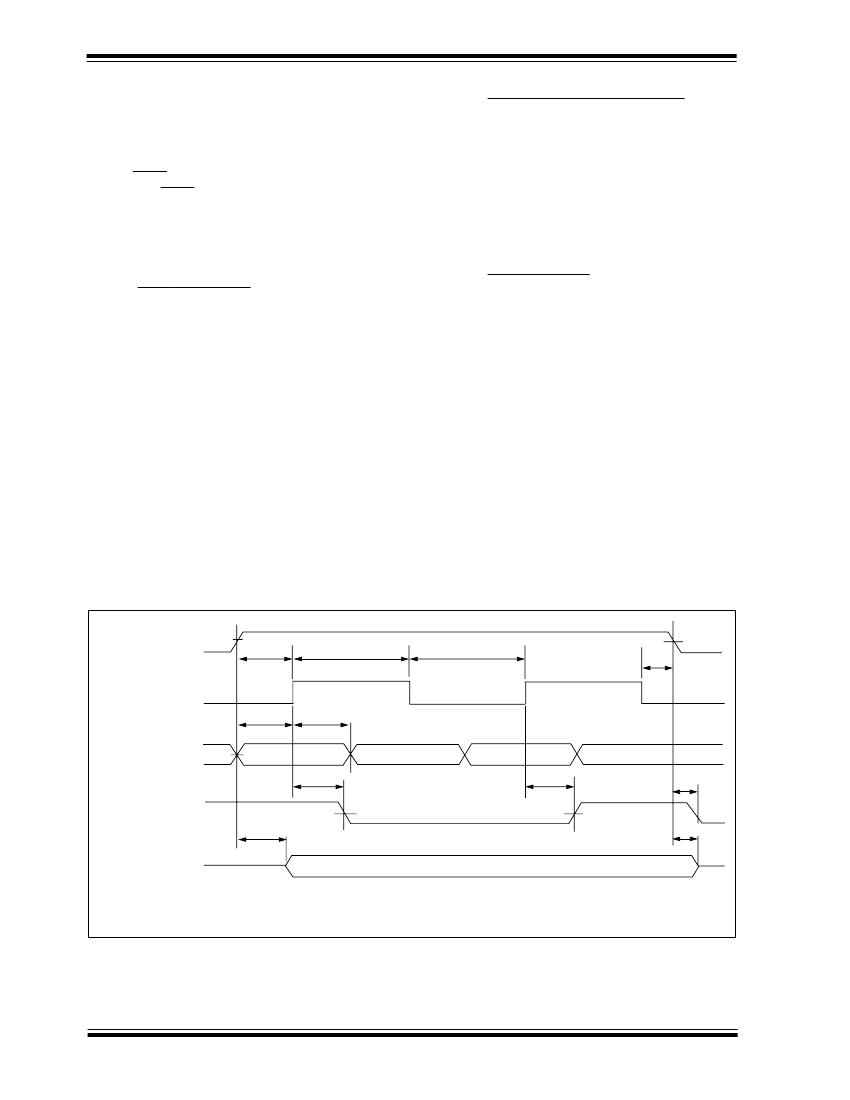

FIGURE 3-1:

CS

SYNCHRONOUS DATA TIMING

V

IH

V

IL

V

IH

T

CSS

T

CKH

T

CKL

T

CSH

CLK

V

IL

T

DIS

V

IH

T

DIH

DI

V

IL

T

PD

T

PD

T

CZ

DO

(READ)

DO

(PROGRAM)

V

OH

V

OL

T

SV

V

OH

T

CZ

STATUS VALID

V

OL

Note:

AC Test Conditions: V

IL

= 0.4V, V

IH

= 2.4V.

DS21207B-page 4

Preliminary

漏

1998 Microchip Technology Inc.