CY7C4421/4201/4211/4221

CY7C4231/4241/4251

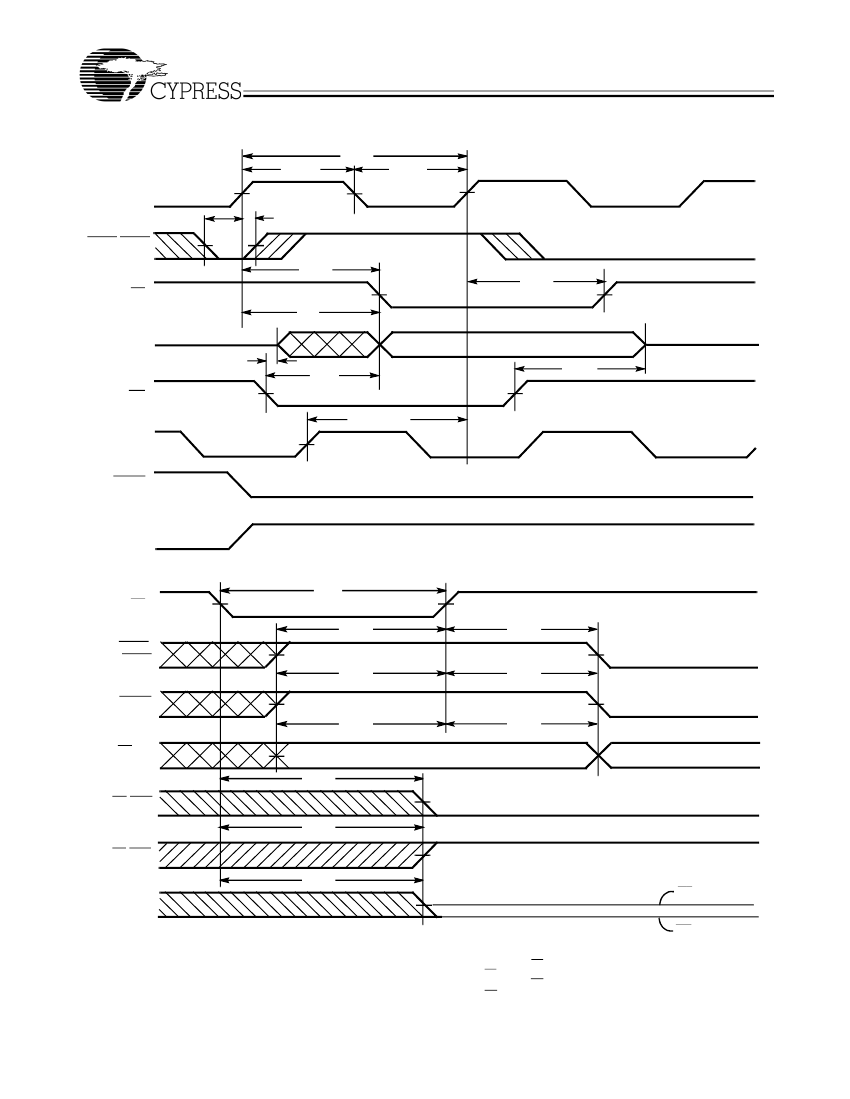

Switching Waveforms

(continued)

Read Cycle Timing

t

CLKH

RCLK

t

ENS

REN1,REN2

t

REF

t

REF

EF

t

A

Q

0

鈥換

8

t

OLZ

t

OE

OE

t

SKEW1

WCLK

[15]

VALID DATA

t

CKL

t

CLKL

t

ENH

NO OPERATION

t

OHZ

WEN1

WEN2

Reset Timing

[16]

t

RS

RS

t

RSS

REN1,

REN2

t

RSS

WEN1

t

RSS

WEN2/LD

[17]

t

RSR

t

RSR

t

RSR

t

RSF

EF,PAE

t

RSF

FF,PAF,

t

RSF

Q

0 -

Q

8

OE=0

Notes:

14. t

SKEW1

is the minimum time between a rising RCLK edge and a rising WCLK edge to guarantee that FF will go HIGH during the current clock cycle. If the time

between the rising edge of RCLK and the rising edge of WCLK is less than t

SKEW1

, then FF may not change state until the next WCLK rising edge.

15. t

SKEW1

is the minimum time between a rising WCLK edge and a rising RCLK edge to guarantee that EF will go HIGH during the current clock cycle. It the time

between the rising edge of WCLK and the rising edge of RCLK is less than t

SKEW1

, then EF may not change state until the next RCLK rising edge.

OE=1

[18]

Document #: 38-06016 Rev. *A

Page 9 of 18