1.表示供应,口碑良好,缴纳了2万保证金,经维库认证中心严格审查。

2.供应商承诺此料号是“现货” ,如果无货或数量严重不足(实际数量不到显示数量一半),投诉成立奖励您500元。

3930

QFP100/2352+

INTEL品牌专卖,一级代理可供更多

带有此标记的料号:

1. 表示供应商具有较高市场知名度,口碑良好,缴纳了2万保证金,经维库认证中心严格审查。

2. 供应商承诺此料号是“现货” ,如果无货或数量严重不足(实际数量不到显示数量一半),投诉成立奖励您500元。

89

TQFP100/1131+

原装现货不仅销售也回收

7963

QFP/24+25+

助力国营二十载,您的原厂窗口,一站式BOM配

5620

QFP100/25+

原厂渠道商,可支持60天账期及180天承兑

12000

-/-

一站式BOM配单服务

EPM7128AETC144-10

165

TQFP/144/0313+

全新原装,现货库存

EPM7128AETC144-10

12850

TQFP144/2135+

军工单位指定合供方/只做原装,自家现货

EPM7128SQC100

1000

BGA/20+

代理渠道,原装现货

EPM7128STI100-7N

4320

PLCC/23+

原装,稳定供货,一站式配齐

EPM7128STC100-15N

5404

TQFP100/23+

原装力挺实单

EPM7128AEFC100-7

5000

BGA/2023+

原厂授权代理 价格优势

EPM7128STI100-10

9007

TQFP100/23+

只售原装,假一罚十

EPM7128AETC144-10

2865

QFP/1608+

特价特价全新原装现货

EPM7128AET

203060

NA/24+

一站配齐 原盒原包现货 朱S Q2355605126

EPM7128SQC100-7

6000

QFP100/21+

原装

EPM7128AETI100-7

34

TQFP100/0337+

原装现货,假一赔十

EPM7128AETI100-7N

36800

QFP100/23+

23+

EPM7128SLI84-10/S

2500

PLCC/15+

全新原装进口现货可开票

EPM7128ELC84-15

10

PLCC/BE124982501+

BE124982501+

EPM7128AEFC256-7

86200

BGA/25+

代理渠道/原装现货,12年老企业承诺原装假一赔百

EPM7128

ETC

EPM7128PDF下载

EPM7128

ETC

EPM7128PDF下载

EPM7128

EPM7128PDF下载

EPM7128

EPM7128PDF下载

EPM7128A

Programmable Logic Device

ALTERA

EPM7128APDF下载

EPM7128A

Programmable Logic Device

ALTERA

EPM7128APDF下载

EPM7128A

Programmable Logic Device

ALTERA [Altera Corporation]

EPM7128APDF下载

EPM7128A

Programmable Logic Device

ALTERA [Altera Corporation]

EPM7128APDF下载

EPM7128B

Programmable Logic Device

ALTERA

EPM7128BPDF下载

EPM7128B

Programmable Logic Device

ALTERA

EPM7128BPDF下载

EPM7128B

Programmable Logic Device

ALTERA [Altera Corporation]

EPM7128BPDF下载

EPM7128B

Programmable Logic Device

ALTERA [Altera Corporation]

EPM7128BPDF下载

EPM7128E

Programmable Logic Device Family

ALTERA

EPM7128EPDF下载

EPM7128E

Programmable Logic Device Family

ALTERA

EPM7128EPDF下载

EPM7128E

Programmable Logic Device Family

ALTERA [Altera Corporation]

EPM7128EPDF下载

EPM7128E

Programmable Logic Device Family

ALTERA [Altera Corporation]

EPM7128EPDF下载

EPM7128S

Programmable Logic Device Family

ALTERA

EPM7128SPDF下载

EPM7128S

Programmable Logic Device Family

ALTERA

EPM7128SPDF下载

EPM7128S

Programmable Logic Device Family

ALTERA [Altera Corporation]

EPM7128SPDF下载

EPM7128S

Programmable Logic Device Family

ALTERA [Altera Corporation]

EPM7128SPDF下载

个差频器74ls74的clk端。经过4个差频器74ls74差频后的频率信号送到可编程逻辑器件epm570gt100c3芯片的i/o口。epm570gt100c3在这里做频率计,通过软件编程来实现。记下的差频频率通过8位数据线送到51单片机at89s52,同时at89s52对epm570gt100c3控制,以选择哪个通道,at89s52处理后的数据经过232串口送到上位机。 以一个通道为例来进行基于qcm传感器的生物芯片检测电路的设计,由于一个通道所使用的逻辑门比较少,因此选择可编程逻辑器件epm7128lc84-10。图1所示是系统总体设计框图。 图1 系统设计总体框图 硬件设计 石英晶体振荡及差频电路 为了保证qcm在滴入生物试剂后能振荡起来,必须采用一套比较特殊的自激振荡器电路,普通的用反相器构成的振荡器电路不易起振,自激振荡器通常是由基本放大电路、正反馈网络和选频网络三部分组成的。在石英晶体振荡电路中,石英晶体作为正反馈网络的主要组成部分,也是一种选频网络,只有在石英晶体振荡器的固有谐振频率下才能满足条件。根据这一原理,采用以max913芯片为核心的振荡器

号经步进电机驱动电路使步进电机行进设定距离。具体实现在软件设计部分介绍。′f240的其他片内i/o、pwm端口、a/d都引出输入输出线,方便扩展功能的实现。 从′f240的特点可以看出,′f240可用于实现复杂控制算法和进行复杂的机器人动作控制。然而根据车体设计方案,需要在车体上安装20个光电检测传感器,占用控制器的20个i/o端口。这样,′f240可用于扩展功能的i/o端口大大减少。机器人在比赛中会有比较剧烈的撞击.如设计各种功能数字电路会严重降低控制板的可靠性。此处选用altem公司的epm7128作为核心处理器的扩展、模糊控制的输入。为满足dsp与cpld之间的协同处理,′f240与epm7128可采用如图2所示的电路连接。′f240的16根数据线和a12~a15共4根地址线连到epm7128,通过选择信号、写信号和读信号完成对epm7128的读写操作。epm7128的i/o端口主要在max+plusⅱ编程环境下通过软件和硬件管脚设置实现。这种dsp+cpld的结构可以在充分扩展系统功能的同时,使dsp更能发挥其运算功能强大的特点。 稳压电路主要由lm7805芯片组成;信号输入电路

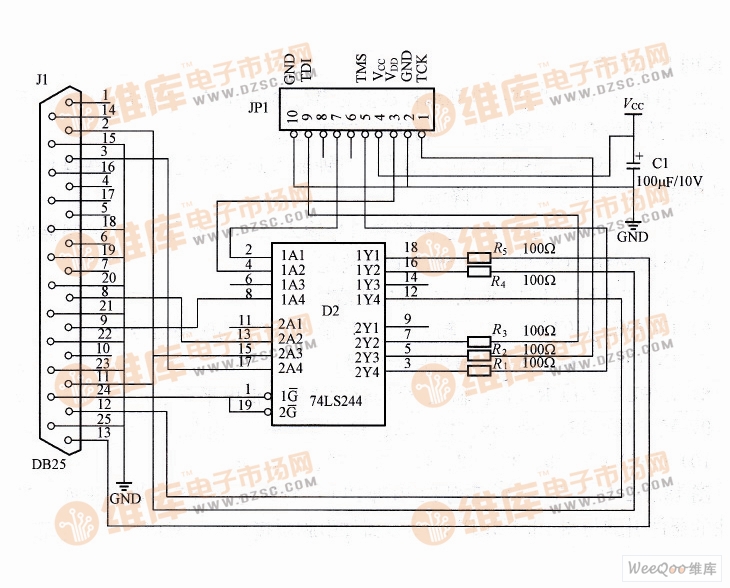

作者email: xuelei_51@126.com 摘要:tms320lf2407a采用了高性能静态cmos技术,使得供电电压降为3.3v,减小了控制器的功耗。但是系统中依然存在很多5v供电的芯片,因此这个系统中就不可避免地存在不同供电电压的模块。为了适应混合电压系统,采用cpld(epm7128)实现dsp(tms320lf2407a)与5v器件接口。 关键词:cpld(cpld);dsp(dsp);混合电压(multivolt)1. epm7128slc84-15简述epm7128slc84-15是altera公司推出的max7000s 系列的cpld(complex programmable logic device);采用cmos e2prom工艺,传输延迟仅为5ns;内部具有丰富的资源--128个触发器、2500个用户可编程门;而且具有68个用户可编程的io口,为系统定义输入、输出和双向口提供了极大的方便;为了比较适合混合电压系统,通过配置,输入引脚可以兼容3.3v/5v逻辑电平,输出可以配置为3.3v/5v逻辑电平输出。epm7128同时还提供了jtag

统成本的考虑,下面的规划不支持pci总线的线性突传输等需要连续几个数据周期的读写方式,而仅支持一个址周期加一个数据周期的读写方式。对于大部分应用而言,这种方式已经足够了。 在cpld内设有13个8位寄存器用来保存进行一次pci总线读写时所需要的数据,其中pci_address0~pci_address3是读写时的地址数据;pcidatas0~pci_datas3是要往pci设备写的数据;pci_cbe[3~0]保存[nextpage]本文相关datasheet:max7000 epm7128 地址周期时的总线命令,pci_cbe[7~4]保存数据周期时的字节使能命令;pci_data0~pci_data3保存从pci设备返回的数据;pci_request是pci总线读写操作状态寄存器,用于向单片机返回一些信息。当单片机往pci_cbe寄存器写入一个字节的时候,会复位cpld中的状态机,触发cpld进行pci总线的读写操作;单片机则通过查询pci_request寄存器得知读写操作完成,再从pci_data寄存器读出pci设备返回的数据。 cpld中状态机的状态转移图如图

可以稳定可靠地运行。 2 硬件部分 pc104到can总线转换卡的硬件系统框图如图1所示。在pc104总线与can总线的通信中,要考虑的主要问题是pc104总线与can总线数据同步问题。pc104总线与can总线的总线速度存在很大差异,针对这样的问题通常采用的方法是使用双端口ram或fifo作为缓冲器,这里使用双端口ram作为数据缓冲,同时在双端口ram中预留几个字节作为atmega64处理器与pc104嵌入式计算机的软握手信号,通过以上方法完成pc104总线与can总线的数据同步。epm7128为altera的cpld,这里使用cpld主要用于pc104到can总线转换卡的地址译码。can总线通信选用sja1000 can总线控制器实现,为了适应工业现场恶劣的电磁环境,在sja1000与pc82c250中经过了光隔处理。 2.1 pc104总线与idt7134接口电路 pc104嵌入式计算机为了读取双端口ram idt7134的数据。首先将idt7134映射到pc104嵌入式计算机的存储器空间,使用smemr*、smemw*作为idt7134的oer,r/w

EPM...

|

1 光栅位移传感器测量原理 基于CPLD芯片EPM7128设计数据合并转换器

|