dds信号发生器功能及原理

出处:互联网 发布于:2017-11-03 15:08:25

DDS( Direct digital synthesis)直接数字频率合成是从相位概念出发直接合成所需波形的一种新的颜率合成技术,它将先进的数字处理理论与方法引入信号合成领域。

DDS信号发生器采用直接数字频率合成(Direct Digital Synthesis,简称DDS)技术,把信号发生器的频率稳定度、准确度提高到与基准频率相同的水平,并且可以在很宽的频率范围内进行精细的频率调节。采用这种方法设计的信号源可工作于调制状态,可对输出电平进行调节,也可输出各种波形。

DDS信号发生器功能

一个完整周期的函数波形被存储在上面所示的存储器查找表中。相位累加器跟踪输出函数的电流相位。为了输出一个非常低的频率,采样样本之间的差相位(Δ)将非常小。例如,一个很慢的正弦波可能将有1度的Δ相位。则波形的0号采样样本采得0度时刻的正弦波的幅度,而波形的1号采样将采得1度时刻的正弦波的幅度,依次类推。经过360次采样后,将输出正弦曲线的全部360度,或者确切地说是一个周期。一个较快的正弦波可能会有10度的Δ相位。于是,36次采样就会输出正弦波的一个周期。如果采样率保持恒定,上述较慢的正弦波的频率将比较快的正弦波慢10倍。 进一步说,一个恒定的Δ相位必将导致一个恒定正弦波频率的输出。但是,DDS技术允许通过一个频率表迅速地改变信号的Δ相位。函数发生器能够指定一个频率表,该表包括由波形频率和持续时间信息组成的各个段。函数发生器按顺序产生每个定义的频率段。通过生成一个频率表,可以构建复杂的频率扫描信号和频率跳变信号。DDS允许函数发生器的相位从到另连续变化。 矢量信号发生器提供高灵活度和强大的解决方案,可用于科学研究,通信,消费电子,宇航/国防,半导体测试以及一些新兴领域,如软件无线电,无线电频率识别( RFID),以及无线传感网络等。 有些公司还提供许多其他利用DAC来产生模拟信号的模拟输出产品。模拟输出板的基本架构是,将一个小型的FIFO存储器连接到一个DAC上。绝大部分的模拟输出板被用来产生静态电压,而且许多可以被用来产生低频波形。

DDS信号发生器工作原理

该技术是根据奈奎斯特取样定理,从连续信号的相位Φ出发,对一个正弦信号进行取样、量化、编码,然后将形成的正弦函数表存入ROM/RAM中,合成时则通过改变相位累加器的频率控制字来改变相位增量,相位增量不同将导致一个周期内取样点数的不同。因角频率ω=△φ·△t,故可在取样频率不变的情况下,通过改变相位累加器频率控制字的方法将这种变化的相位/幅值量化为数字信号,然后通过D/A变换和低通滤波即可得到相位变化的合成模拟信号频率。该技术是根据奈奎斯特取样定理,从连续信号的相位Φ出发,对一个正弦信号进行取样、量化、编码,然后将形成的正弦函数表存入ROM/RAM中,合成时则通过改变相位累加器的频率控制字来改变相位增量,相位增量不同将导致一个周期内取样点数的不同。因角频率ω=△φ·△t,故可在取样频率不变的情况下,通过改变相位累加器频率控制字的方法将这种变化的相位/幅值量化为数字信号,然后通过D/A变换和低通滤波即可得到相位变化的合成模拟信号频率。

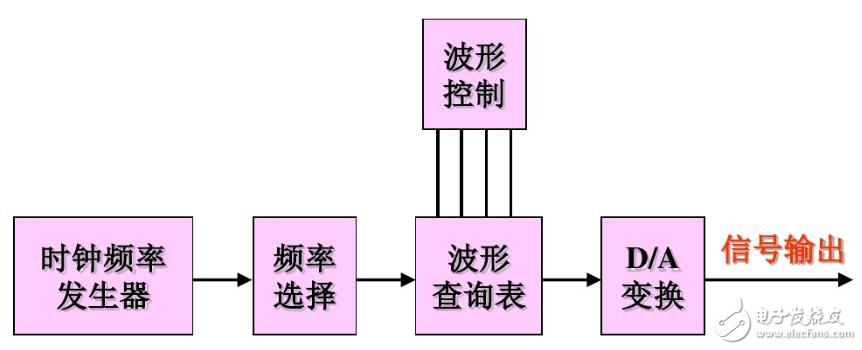

上图是DDS的基本原理框图,它主要由四部分组成:

部分为相位累加器,用于决定输出信号频率的范围和;

第二部分为正弦函数功能表(波形存储器),用于存储经量化和离散后的正弦函数的幅值;

第三部分为D/A转换,可产生所需的模拟信号;

第四部分为低通滤波,用来减少量化噪声、消除波形尖峰。

参考频率源是一个高稳定度的晶体振荡器,用以同步DDS中各部件的工作,因此,DDS输出的合成信号的频率稳定度和晶体振荡器是一样的。从原理上还可看出,它是用高稳定的固定时钟频率来对所要合成的信号进行相位取样的,单位时间内取样量越大,则合成的频率越低。取样量的大小由可程控的频率设定数据决定。

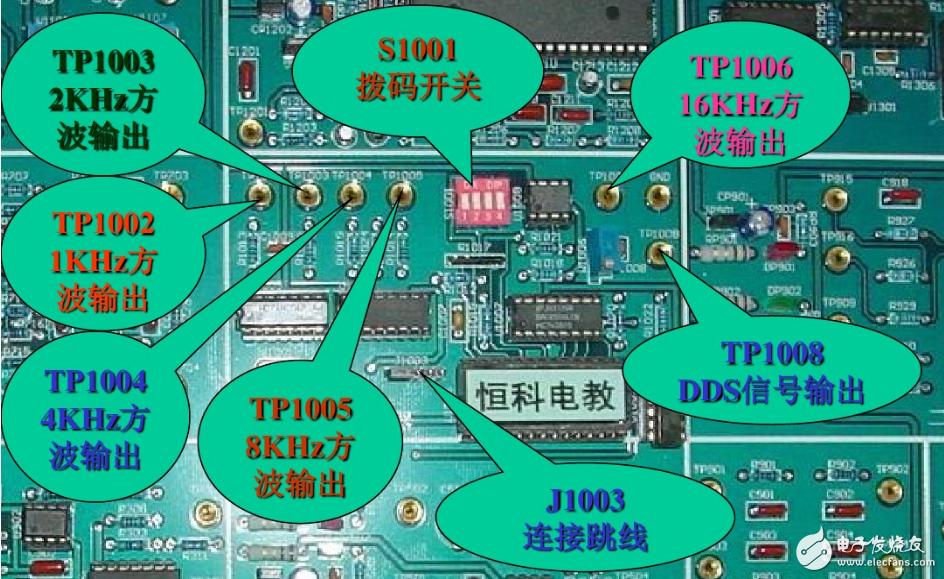

DDS信号发生器结构原理

参考频率clock为整个合成器的工作频率,输入的频率字保存在频率寄存器0或1中,经32位相位累加后,再和相移寄存器累加以得到内部ROM的地址,然后经过内部ROM正弦波形表便可得到相应的幅度值,经过D/A转换和低通滤波器得到合成的正弦波。 3.189C52和AD7008接口设计3.3正交信号形成电路设计

AD7008为单片DDS集成芯片,其结构如图所示。该器件内含32位相位累加器、正余弦查找表及10位DAC的DDS调制器,时钟频率可达20~50MHz;还内含两个10位乘法器、20位IQMOD寄存器及12位相位寄存器。除了可合成正弦波外,还可实现调频、调相、调幅及数字解调,同时提供了可与微机接口的并行和串行接口。

由于AD7008的相位累加器为32位,故2π=232,则△phase必须在0≤△phase≤232-1的范围内,每一时钟周期,32位累加器累加一个相位阶距,输出频率fout为:fout=△phasefclock/232

式中,fclock是参考频率。实际使用中,fout的上限取fclock的40%(考虑到相位噪声和杂散信号干扰 ) 即△phase上限取0.4&mes;232。△phase可通过控制FSELECT从FREQ0、FREQ1中选择。尽管AD7008包含有32位相位累加器,但其输出仅为12位,因此没有必要也不可能用32位的分辨率。12位的相位数据经查询可转换成10位幅度信号。如果不要求调幅,IQ乘法器可以被旁路(CR2=0),而将正弦信号幅值直接送往DAC电路。通过外电阻Rset可对DAC满量程输出电流进行调节,公式如下:

Iout(mA)=6233Vref(V)/Rset(Ω)

上一篇:ad9854产生线性调频脉冲信号

下一篇:rake接收机的工作原理

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 锁相环的基本概念2024/4/23 17:56:14

- 信号与系统分析简介2024/4/16 17:03:33

- 使用逻辑信号、交流耦合和接地栅极驱动 CMOS 图腾柱2024/4/10 16:54:32

- 什么是射频?什么是射频信号?2024/4/7 17:53:28

- 探索光耦合器替代方案2024/3/29 17:04:49

- 英特尔数据存储如何操作和实现

- 什么是微动开关_微动开关有什么用_微动开关使用方法

- VCC,VDD,VEE,VSS在电源原理图中有什么区别?

- 低压配电系统设计规范_低压配电系统设计注意事项

- xEV 主逆变器电源模块中第四代 SiC MOSFET 的短路测试

- 光耦详细应用教程

- 定义绝缘耐久性评估的电压脉冲测试要求

- 采用沟槽MOS结构,使存在权衡关系的VF和IR相比以往产品得到显著改善 ROHM推出实现业界超快trr的100V耐压SBD“YQ系列”

- NOVOSENSE - 纳芯微推出车规级温湿度传感器NSHT30-Q1,助力汽车智能化发展

- Keysight - EV 电池设计创新:扩大续航里程、延长电池寿命