信息存储器模块的电路图

出处:维库电子市场网 发布于:2014-03-07 09:35:56 | 3664 次阅读

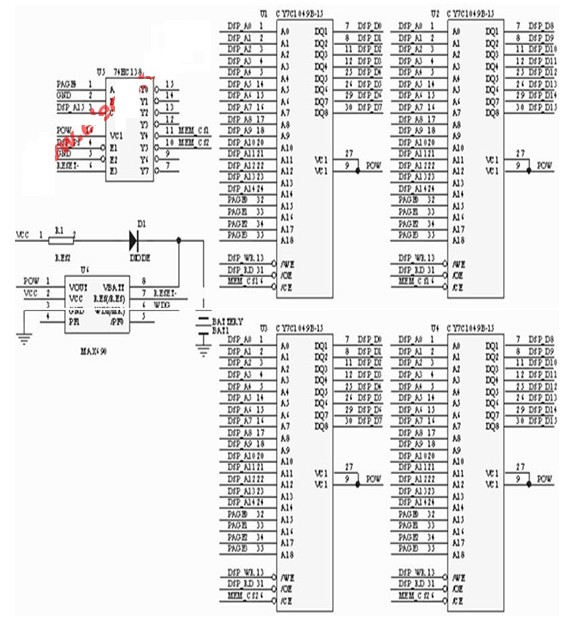

由于ARM的读写速度很快,防止ARM访问片外存储单元出现“瓶颈”现象,应选用快速存储器芯片,不需要ARM插入等待状态,只要将存储器芯片的地址线、数据线与MC9328MX1的数据线、地址线相连,再辅以必要的控制信号和译码电路,就可以使ARM全速运行。在系统中,我们选用4片CY7C1049B-15 SRAM(512K X 8bits)用作信息存储器,再附加上掉电保护电路,将其构成1M字存储单元。它在系统中分配的存储地址为8000H-FFFFH单元(注:0000H-7FFFH为其它存储用),故1M字存储单元共可分成1M/32K=32个页面。其中页面寄存器利用可编程器件FPGA设计实现。信息存储器模块的电路图如下图所示。

下一篇:存储器的原理电路图

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

![810电脑主板电路图1[_]33](https://image.dzsc.com/diagram/2011/05/19/20110519175121828.jpg)

![电脑主板 810 3[_]10芯片组](https://image.dzsc.com/diagram/2011/05/19/20110519175335125.jpg)

![电脑主板810E电路图[_]24](https://image.dzsc.com/diagram/2011/05/19/20110519181051985.jpg)