嵌入式系统的PCI Express时钟分配

出处:libo_feng 发布于:2010-02-23 10:48:11

PCI Express (PCIe)是嵌入式和其它系统类型的背板间通信的一个非常理想的协议。然而,在嵌入式环境中,背板连接器引脚通常很昂贵。因此,采用点对点连接的星型结构的PCIe时钟分配方案就变得并不理想。本文将讨论如何使用一个多点信号来分配PCIe时钟,而且仍满足PCIe第二代规范严格的抖动要求。

PCIe计时

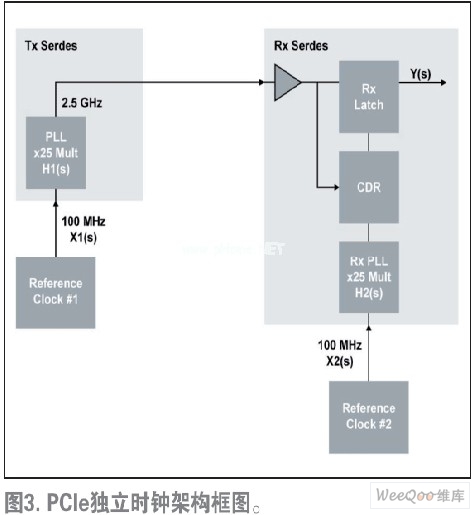

PCIe基本规范1.1和2.0为信令速率2.5Gbps和5.0Gbps的时钟分配定义了三个不同模型,见图1、图2和图3。

共用时钟架构作为常使用的方法有很多理由。首先,大多数支持PCIe接口的商用芯片只适用于这种架构。其次,这种架构是可以直接支持展频计时(Spread Spectrum clocking,简称SSC)的架构。SSC在减少电磁干扰峰化方面起着非常重要的作用,因此可以简化符合系统电磁辐射限制的工作(见图4)。,这种架构容易形成概念和设计。

共用时钟架构的缺点在于需要为系统中每个PCIe端点分配基准时钟。频率为 100MHz或125MHz的时钟以及PCIe规范严格的抖动要求使得这一架构变得尤其复杂。对2.5Gbps工作的限制为86ps——106采样的一系列样本的峰-峰相位抖动。而5.0Gbps工作的限制为3.1ps(均方根抖动值)。然而,要在5.0Gbps工作,收发器首先要在2.5Gbps协商,如果两端都可以,再提高到5.0Gbps。这就是说如果系统支持任何5.0Gbps链接,则基准时钟就必须同时满足两者的抖动指标。

独立的数据时钟架构不会受到上述限制,但却大幅增加了时钟系统设计的复杂性,且在不使用单边带信令时不支持SSC。

基准时钟抖动的管理规范是PCIe基本规范1.1和2.0,而检验抖动达标的方法详细列在PCIe抖动建模修订版1.0D和PCIe抖动和BER修订版1.0中。机电规范提供了机械尺寸信息、电信号定义和功能。其中一些,如卡机电(Card Electromechanical,简称CEM)1.1和CEM2.0规范也为基准时钟、Tx锁相环(Phase-Locked Loop,简称PLL)、Rx PLL和介质提供了抖动预算。严格来讲,CEM规范只申请了PC和服务器ATX,以及基于ATX的尺寸。其它已出版的机电规范覆盖了其它尺寸,如用于移动计算平台的Mini Card Electromechanical Specification 1.2。

对于大多数嵌入式系统,上述这些规范可以全部或部分用来规定嵌入式系统PCIe时钟分配方案提供指南。例如,许多CEM文件规定了对基准时钟分配Host ClockSignal Level(HCSL)协议的使用。然而,许多嵌入式系统希望使用低电压正射极耦合逻辑(Low Voltage Positive Emitter Coupled Logic,简称LVPECL)或多点低电压差分信号(Multipoint-Low-Voltage Differential Signaling,简称M-LVDS)信令,以实现时钟分配网络更远的距离和/或噪声容限。

许多嵌入式系统需要在其背板之间分配包括时钟在内的大量高速信号。为了解决这些背板上经常出现的繁重电气负载问题,这些信号需要有非常强大的驱动器和高边缘速率。这带来了干扰和其它信号完整性的危险,尤其是在背板比差设计点的负载更低时。另一个设计上的挑战在于PCIe详细规定了100MHz或125MHz的基准时钟,这是一个很难在高负载长背板上顺利分配的频率。

除了PCIe规范严格的抖动限制和需要更长的信号距离,嵌入式系统通常还受到可能通过背板连接器和背板本身的信号量的限制。当定制系统时,确定连接器引脚排列是关键的任务之一。

建议的共用时钟分配方案

由于时钟频率和抖动限制,常见的共用时钟架构设计利用点对点差分信号对来分配基准时钟,其中一个差分信号对将抵达系统的每个PCIe端点。如果一张卡上有多个PCIe端点,就可以从背板获得一个基准时钟输入,并利用零延迟缓冲器(Zero Delay Buffers,简称ZDB)提供卡上时钟分配网络。然而,即使这样,由于PCIe 5.0Gbps运行的抖动限制,设计起来也是非常困难的。

假设我们能设计出这样的卡上分配方案,我们仍需要提供从PCIe主到系统上每张卡的点对点连接。在嵌入式系统中,这需要在主卡插槽上增加大量连接器引脚,并在背板上增加大量有特殊布线要求的线迹。这还要给主卡插槽插入与其它插槽截然不同的引脚排列。

一个消除这些限制的解决办法是降除主卡上的PCIe基准时钟,并利用一个M-LVDS多点信号在背板之间进行分配,然后将其提高到目标卡所需的频率。尽管理论上非常简单,但实现PCIe抖动限制却很棘手(见图5,注意绿色信号线不起作用)。

这一解决方案可提供一个M-LVDS对,用来驱动或接收符合PCIe的基准时钟。如图5所示,在许多嵌入式系统中,根据应用的”与/或”插槽进行分配,每张卡都可作为主操作或端点操作。显然,如图所示,只用于其中一种模式操作的卡将被简化。系统中的一张卡将作为主,利用其板上晶振生成满足PCIe限制的基准时钟。这个时钟将利用内部时钟分配网络驱动所有板上PCIe器件。该时钟也将到达非PLL除法器电路,将100MHz或125MHz向下降除为25MHz的背板频率,然后将除降了的基准时钟驱动到系统的其余卡上。

系统中其它所有的卡将禁用板上时钟发生器,形成基准时钟线迹的三态驱动器,并接收来自背板的基准时钟。随后,这将通过基于PLL的ZDB提高到板上所需和分配的基准时钟频率,并将划分了的基准时钟驱动到系统的其它卡上。系统其它所有的卡将失去对板上时钟发电器的使用,形成基准时钟线迹三态驱动器,并接收来自背板的基准时钟。这将通过基于PLL的ZDB提高到板上和分配所需的基准时钟频率。接收和提高来自背板的基准时钟的电路通常在主卡上,如果需要,可以用来生成所需的另一个基准时钟频率。为了实现PCIe所需的低抖动,IDT FemtoClock PLL技术可用于时钟合成器和ZDB。

像这种设计的主要难点之一在于,PLL虽然可以过滤掉频率高于PLL本身环路带宽的噪声信号,但在低于PLL环路带宽的低频部分,却增加了很多在调制频率附近的附加抖动。另外,由于PLL无法完全跟踪基准时钟输入的相位和频率变化,从而引起跟踪偏移。像这种包含两个以上用于频率生成和转换的级联型PLL的背板PCIe方案必须谨慎对待,以尽量降低相位抖动和PLL跟踪偏移。

PCIe抖动的测量

在深入分析这个解决方案的性能之前,需要先讨论PCIe抖动性能的分析过程。 PCIe抖动工作组关注的一个首要问题是确定一个恰当的基准时钟。为了这个目的,需要考虑基准时钟的Tx和Rx PLL及相位插值器的过滤效果。同时,为了避免对基准时钟规格不足,这些PLL的峰值效应也需要考虑。这一过程分为四个主要步骤:

1. 确定每个周期累积的相位误差。串行数据传输不像并行数据传输那样关心时钟的Cycle-to-Cycle抖动和Period抖动,串行数据传输更关心累积相位误。因此,我们必须首先确定每个时钟周期的累积相位误差。

2. 将离散傅立叶变换(Discrete Fourier Transform,简称DFT)用于累积相位误差数据,从而将时域的分析转变到频域进行分析。

3. 将系统转移函数用于累积相位误差数据的DFT。

4. 执行逆DFT,使过滤后的累积相位误差数据转回到时域内,这便是终结果。

同时还要注意,通过设定系统转移函数s=jω,可以在复杂的频域实现PLL系统的过滤分析。该分析对连续系统很有用,但由于采用相位检测器和反馈除法器等数字元件,大多数现代PLL方案不是纯粹的模拟系统,因而z域数字分析会更。但是,PCI抖动工作组的初步研究表明,受s域分析影响的误差,因此s域分析可用于建模。然而,当基频低于PLL环路带宽十倍时,s域近似值会显著背离真值。所以系统设计师在选择PLL时必须时刻谨记这一点。

抖动测量技巧

测量方法不当很容易得到两倍以上于正确方法的抖动测量值。这里有一些技巧:

从被测器件到示波器都使用屏蔽同轴电缆,并在示波器的输入端做好恰当的匹配。

1. 如果使用高阻抗探头,可使用低电容探头和接地夹,而非电线。

2. 确保你使用了与样本量一致的采样率。

3. 使示波器屏幕上的纵坐标,以便地测量电压。

4. 使显示器、开关式电源和手机远离被测器件。可行时使用线性电源。

5. 当执行差分测量时,确保两条电缆已经相互纠偏。

IDT解决方案分析

IDT的工程师通过菊链三个特性描述板以代表子卡:ICS841S32I板,然后是ICS8743008I板,一个也是ICS8743008I板,创建了解决方案的原型,见图5。在第二个ICS8743008I输出时进行测量。卸载来自示波器的时钟周期数据,然后由抖动分析脚本进行后处理。该脚本可进行必要的频域和时域分析。

2.5Gbps分析方法的结果为18.91ps。这一结果符合4.5倍的裕量的 86ps的PCIe峰-峰相位抖动指标。对于5.0Gbps操作,PCIe规定了rms相位抖动,而非峰-峰相位抖动。这些结果也超出了规范: 0.52ps rms低频带和1.47ps高频带与3.1ps规范限制之比。

对于5.0Gbps工作,PCIe为频域分析规定了两个转移函数和两个频率范围。个转移函数的极频率为5MHz和16MHz,第二个转移函数的极频率为8MHz和16MHz。抖动分析所得的两个频段为10KHz-1.5MHz(低频带),1.5MHz-Nyquist(高频带)。Nyquist表示你的分析达到了基准时钟频率的一半。例如,在100MHz时,频域分析将达到 50MHz。分析脚本会显示每个频率分析频带间两个转移函数间的差情况。

结束语

PCIe标准初用于定义PC系统,但由于其低引脚数和可扩展的高性能,很快成为几乎所有应用领域选择的I/O接口。高速的基准时钟给希望利用PCIe元件的嵌入式系统工程师们提出了严峻的挑战。他们需要分配、选择两个不同的、符合规范的基准时钟速度。

其中一个测试解决方案有助于系统利用支持100MHz和125MHz基准时钟的元件,并通过一个M-LVDS差分对将其分配到系统的所有卡上。这一解决方案也可以对卡进行设置,因此这些卡可以在其应用指令下作为主或端点操作,而且能插入系统的任何插槽。另外,这一解决方案降低了背板上基准时钟的工作频率,放宽了该信号的路由限制和串扰性能。只要满足2.5Gbps和5.0Gbps操作 PCIe规范严格的抖动要求,所有这些都可以用一个设计实现。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- EPS Global - 谁需要嵌入式安全?2024/4/22 15:39:31

- 什么是嵌入式SoC2024/4/3 16:20:28

- EasyARM-i.MX283(7)A 默认供电方案2024/3/28 17:39:53

- EasyARM-i.MX283(7)A 的快速入门2024/3/27 17:29:30

- 非线性数字滤波器:用例和示例代码2024/3/14 16:34:20