基于EPM3128的HDB3编译码器的实现

出处:electron1 发布于:2011-09-23 11:33:43

摘要: 数字基带信号的传输是数字通信系统的一个重要组成部分, H DB3 编码是数字基带信号传输中常用的传输码型。本文介绍了HDB3 编码规则, 提出了一种基于EPM3128 实现编译码的方法, 该方法具有成本低、电路简单、执行速度快、升级方便等特点。同时由于CPLD 可重复编程的特点, 可以对它进行在线修改, 便于设备的调试和运行。此编译码器已经过实际测试, 运行稳定可靠, 可用于实际电路中。

0 引 言

数字基带信号的传输是数字通信系统的重要组成部分。

在数字基带传输系统中, 从信源输出的信号一般是用“ 0” 、“ 1”两种状态表示的单极性不归零码( NRZ 码) 。在进行数字信号基带传输时, 必须考虑到传输信道的特点, 将信息比特变换为适合于信道传输的数字信号, 即进行线路编码。传输线路对码型的基本要求为:

1) 容易提取定时信号;

2) 不含有直流分量;

3) 低频成分和高频成分应尽量减少;

4) 设备简单、容易实现编解码。

而HDB3 码因其无直流成分、低频成分少和连0 个数多不超过3 个等特点, 而对定时信号的恢复十分有利, 并已成为CCITT 推荐使用的基带传输码型之一, 在实际的数字基带传输中有着非常广泛的应用。

本文选用Altera 公司EPM3128 作为主控芯片, 详细介绍了一种实现数字通信系统中的HDB3 码编译码的实现方法。

主控芯片EPM3128AT C100 10 是一款高性能、低功耗、基于EEPROM 的CPLD, 片内集成了2500 个可用门,8 个逻辑阵列模块( LAB) , 每个LAB 由16 个宏单元组成, 多为用户提供80 个I /O 口, 通过JT AG 接口进行在线编程, 可以进行100 次的程序烧写。A LTERA 器件采用铜铝布线的先进CMOS 技术, 功耗低、速度快, 采用互连结构, 提供快速、连续的信号延时和具有相同延时的时钟总线结构。逻辑集成度高, 开发周期短, 使用专用软件设计输入、处理、校验及器件编程一共仅需几个小时。FPGA /CPLD 中寄存器资源或组合逻辑资源比较丰富, 更适合于时序电路和组合逻辑电路的设计。

1 HDB3 码的编码规则

HDB3 码是AMI 码的改进型, 称为三阶高密度双极性码, 它克服了AMI 码的长连0 串现象。HDB3 码的编码规则如下:

1) 将消息代码变换成AMI码

2) 检查AMI 码中0 的情况。当无4 个或以上的连0串时, 则保持AMI 码的形式不变。当出现4 个或以上的连0 串时, 则将1 后的第4 个0 变为与前一非0 符号同极性的符号, 用V 表示( + 1 记为+ V, - 1 记为- V) 。

3) 检查相邻V 符号间的非0 符号的个数是否为偶数, 若为偶数, 则再将当前的V 符号的前一非0 符号后的第1 个0 变为+ B 或- B 符号, 且B 的极性与前一个非0符号的极性相反, 并使后面的非0 符号从V 符号开始再交替变化。

2 HDB3 编码器的建模与实现

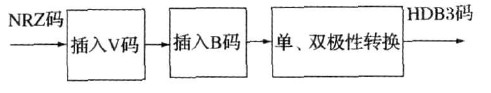

HDB3 码的编码过程, 依据其编码算法可以分成三个步骤步完成: 1) 、插入V 码; 2) 、插入B 码; 3) 、单极性码到双极性码转换。其编码模型如图1 所示。

图1 H DB3 编码器模型

2. 1 插V码模块

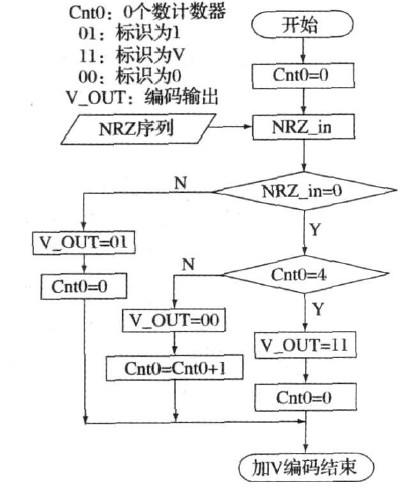

插V 模块的功能是对输入的NRZ( 单极性不归零码)消息代码中的4 连0 串的检测, 只要出现4 个连0 串时候, 把第4 个0 变换成符号V ( V 是逻辑1 高电平) , 而在其他情况下, 则保持消息代码的原样输出。在插V 过程中, 为了区分不同的码( 0、1、V 码) , 我们分别用11 标识“ V ”, 用01 标识“1” ,用00 标识“ 0” 。对输入的NRZ 码编码的算法如图2 所示。

图2 插V 码的流程

2. 2 插B 模块的实现

插B 模块的功能是保证附加V 符号后的序列不破坏极性交替反转的规律, 使输出信号频谱无直流分量。

根据编码规则, 当相邻V 符号之间有偶数个非0 符号时,把后一小段的第1 个0 变换成一个非破坏符号( B 符号,为了区分其它码, 用?? 10 表示) 。图3 所示为实现插B 功能的流程图。根据HDB3 码编码规则, 图3 中插B 模块因为涉及到一个由现在事件的状态决定过去事件状态的问题, 因此需要把输入的信号延时3 个时钟周期, 可以用3个串联的D 触发器来实现信号的锁存。

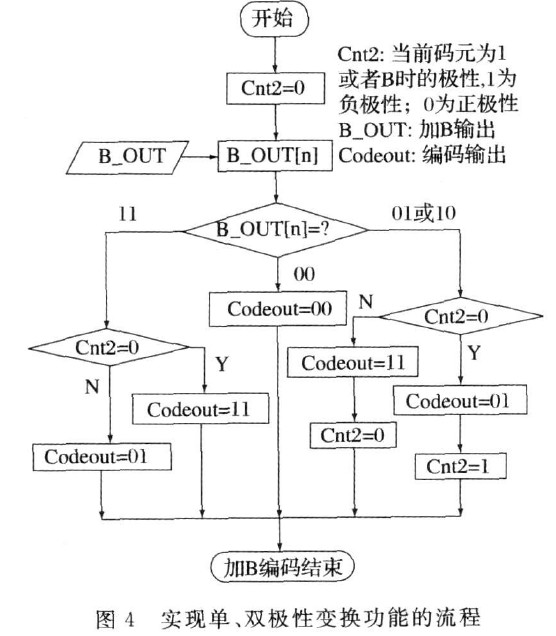

2. 3 单极性变双极性的实现

根据HDB3 编码规则, 我们知道B 符号的极性与前一非零符号相反, V 极性符号与前一非零符号一致。因此, 可对V 单独进行极性变换(V 已经由11 标识, 相邻V 的极性是正负交替的) , 余下的1 和B 看成一体进行正负交替, 从而完成HDB3 的编码。由此我们可以将其分别进行极性变换来实现。从前面的算法可知,“V ”、“ B” 、“ 1” 已经分别用双相码“11” 、“ 10” 、“01 ”标识。所以通过图4 的算法可以很容易实现极性的转换。这个部分遇到的问题是在Quar tusII软件仿真过程中, 它无法识别- 1, 因为它是一个二进制仿真系统, 在它的波形仿真中只有“1” 和“0 ”两种状态。因此,这里采用了双相码来分别表示“ - 1” 、“+ 1” 、“ 0 ”, 即“ - 1” 、“ + 1” 、“ 0 ”分别用“11 ”、“ 01 、“ 00 ”表示。

3 HDB3 编码器的仿真

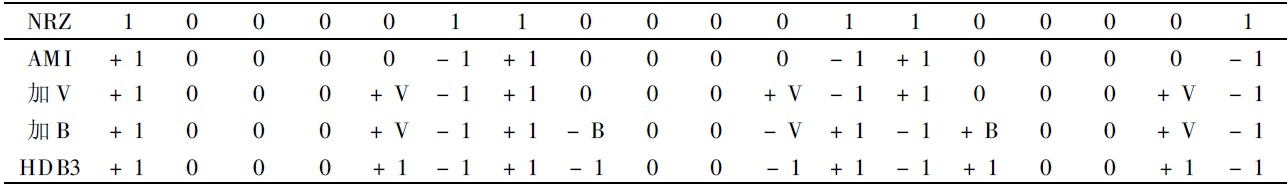

HDB3 编码器顶层结构图如图5 所示。我们利用表1所示的多连零NRZ 消息代码进行分析, 并利用EDA 工具对源程序进行编译、适配、优化、逻辑综合与仿真。图6~ 8 分别为插V 码仿真波形图、插B 码仿真波形图、极性转换仿真波形图。图9 为系统编码器仿真波形图。各个子模块及系统仿真结果显示其完全可以达到编码要求。

表1 HDB3 编码举例

但此时我们应该注意到EPM3128 输出的编码并不是真正意义上的HDB3 编码, 这里采用了“11”、“ 01” 、“ 00 ”来分别表示“ - 1” 、“ + 1” 、“ 0 ”。HDB3 码是一个三电平变化波形, 不能单纯依靠数字电路完成, 应此我们还要利用多路模拟开关CD4052 把“ 11 ”、“ 01 ”、“ 00 ”分别转换成- 1、+1、0。因这部分内容比较简单, 不在叙述, 请参考CD4052数据手册。

4 HDB3 码的译码规则

HDB3 码的译码是编码的逆过程, 其译码相对于编码过程较简单。从其编码规则可知, 每一个破坏符号V 总是与前一非0 符号同极性。因此从收到的HDB3 码序列中, 我们容易识别V 符号, 同时也肯定V 符号及其前面的3 个符号必是连0 符号, 于是可恢复成4 个连0 码, 然后再将所有的- 1 变成+ 1 后便得到原消息代码。

5 结束语

本文分析了HDB3 编译码的特点, 提出了一种基于CPLD 器件的HDB3 编码器及译码器的新的实现方法, 并在到Altera 公司的EPM3128AT C100 10 上, 进行了验证和测试。目前, 很多NRZ 码到HDB3 码的编译码电路大都是用特定功能的芯片加外围器件构成。而本文设计的系统可以代替多个集成芯片和外围离散器件来完成编译码任务, 提高了H DB3 编译器的集成度及信号传输的可靠性。另外, 可编程逻辑器件可反复编程的灵活性, 也便于对HDB3 编译器进行相应的功能扩展和维护。

参考文献:

[1]. CPLD datasheet https://www.dzsc.com/datasheet/CPLD+_1136600.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 模糊逻辑在 DSP 上实时执行2023/7/25 17:13:30

- 多速率DSP及其在数模转换中的应用2023/6/12 15:28:52

- 使用 DSP 加速 CORDIC 算法2023/3/29 15:46:30

- 高速DSP系统的信号完整性2022/9/26 16:45:38

- 自适应噪声消除系统的实现2022/1/17 17:51:17