一种FIR滤波器的DSP设计和实现

出处:山西电子技术 发布于:2011-09-04 13:14:38

数字滤波器是一个离散时间系统(按预定的算法,将输入离散时间信号转换为所要求的输出离散时间信号的特定功能装置)。应用数字滤波器处理模拟信号时,首先须对输入模拟信号进行限带、抽样和模数转换。数字滤波器输入信号的抽样率应大于被处理信号带宽的两倍,其频率响应具有以抽样频率为间隔的周期重复特性,且以折叠频率即1/2抽样频率点呈镜像对称。为得到模拟信号,数字滤波器处理的输出数字信号须经数模转换、平滑。数字滤波器具有高、高可靠性、可程控改变特性或复用、便于集成等优点。数字滤波器在语言信号处理、图像信号处理、医学生物信号处理以及其他应用领域都得到了广泛应用。数字滤波器有低通、高通、带通、带阻和全通等类型。它可以是时不变的或时变的、因果的或非因果的、线性的或非线性的。应用广的是线性、时不变数字滤波器,以及FIR滤波器 。

1 FIR滤波器基本结构

FIR滤波器:有限长单位冲激响应滤波器,是数字信号处理系统中基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

FIR滤波器的数学表达式为:

式中:N为FIR滤波器的抽头数;x(n)为第n时刻的输入样本;h(i)为FIR滤波器第i级抽头系数。

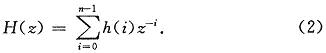

其相应的z变换为:

式中:z-i为N-1阶多项式。

普通的直接型FIR滤波器结构如图1所示。

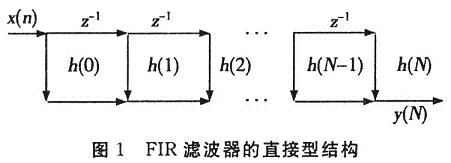

在自适应处理、数据通信等领域中往往要求信号在传输过程中不能有明显的相位失真,FIR滤波器可以做到线性相位满足此要求。F1R滤波器实质上是一个分节的延迟线,把每一节的输出加权累加,得到滤波器的输出。对于FIR滤波器的单位脉冲响应h(i)只要满足以下2个条件之一,则为线性相位滤波器。

线性相位的FIR滤波器具有中心对称的特性,其对称中心在N/2处。

![]()

(2)由性能指标确定窗函数w(n)和窗口长度N

(3)求得实际滤波器的单位脉冲响应h(n)

![]()

(4)检验滤波器性能。

设计常用的窗函数有矩形窗、汉宁窗、海明窗、凯撒窗等。其中:海明窗的旁瓣峰值小于主瓣峰值的1%,99.963%的能量集中在主瓣内.且通过海明窗设计的FIR滤波器在较少的阶数下可以得到较小通带纹波,非常适合工程设计,所以本设计选择海明窗实现。

FIR的特点

有限长单位冲激响应(FIR)滤波器有以下特点:(1) 系统的单位冲激响应h (n)在有限个n值处不为零;(2) 系统函数H(z)在|z|>0处收敛,极点全部在z = 0处(因果系统);(3) 结构上主要是非递归结构,没有输出到输入的反馈,但有些结构中(例如频率抽样结构)也包含有反馈的递归部分。设FIR滤波器的单位冲激响应h (n)为一个N点序列,0 ≤ n ≤ N —1,则滤波器的系统函数 H(z)=∑h(n)*z^-n 就是说,它有(N—1)阶极点在z = 0处,有(N—1)个零点位于有限z平面的任何位置。

3 利用QEDesign Lite设计FIR滤波器

根据窗函数设计的FIR滤波器的单位脉冲响应.h(n)有多种辅助工具进行求取,如:MATLAB的FDATool、SPTool和NI的Digital Fliter Design Toolkit等,在此.我们使用了FreeScaleDSP开发环境Codewarrior8.O自带的QEDesignlite滤波器设计工具箱进行FIR滤波器单位脉冲响应h(n)的求解。

利用QE Design lite滤波器设计工具箱,可快速进行IIR滤波器、基于窗函数FIR滤波器和等纹波FIR滤波器的低通、高通、带通和带阻设计。并根据设计参数,自动生成滤波器的幅频响应、相频响应、群延时、冲击响应和单位阶跃响应,以及生成单位脉冲响应h(n)的*.h文件和该FIR滤波器使用示例C文件,以方便后续设计。其主要设计步骤如下:

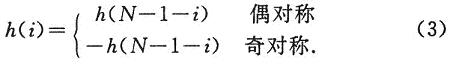

(1)运行程序QEDesign lite,选择菜单项“DesignI FIRWindows Design……”:

(2)在弹出的“FIR(Windows)Design”窗体中,选择“lowpass”选项;

(3)在“Lowpass Filter”窗体中,输入FIR滤波器的设计指标:采样频率=20000 Hz、通带频率=5000 Hz、阻带频率=6000 Hz、通带纹波=O.01 dB和阻带纹波=40 dB.如图2所示;

(4)确定采用的窗函数类型及阶数(本例采用hamming窗.阶数为27阶);

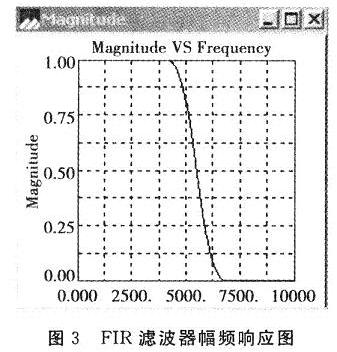

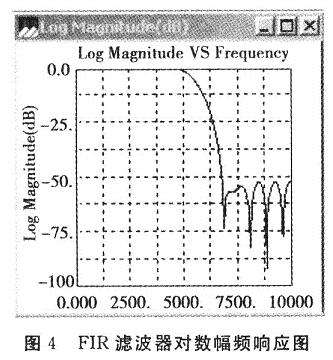

(5)根据设定的FIR滤波器参数,即可得到该FIR滤波器的幅频响应图、对数幅频响应图、相频响应图、群延时图、冲击响应图和单位阶跃响应图,可直观的观察设计是否满足要求.如果不满足设计要求,可重复步骤3)、4),直至满足设计要求为止。本FIR滤波器的幅频响应图、对数幅频响应图见图3、图4;

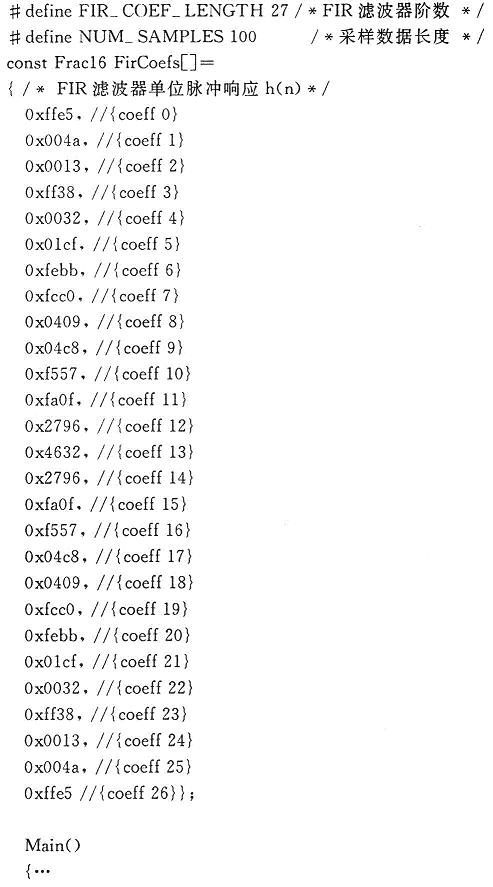

(6)设计的FIR滤波器满足要求后,选择菜单项“Code-Gen|FreeScale|DPS56800/DPS56800E”,导出基于16位定点数的单位脉冲响应h(n)的*.h文件,用于后续的工程设计。

4 基于56F8013 DSP的设计实现

56F8013是FreeScale推出的基于56F800E内核的低价位、低功耗的16位DSP,它具有I2C、SPI、UART、ADC、QEI等外部接口,具有在片硬件调试接口,可进行32位整数、36位整数加分数运算,配合CodeWarrior开发环境非常适合于嵌入式开发。

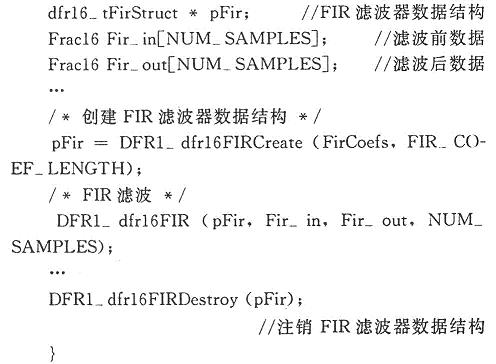

Processor Expert(PE)是由捷克UNIS公司开发的针对FreeScale单片机和DSP的嵌入式软件开发包.它集成在CodeWarrior开发环境中。Processor Expert提供了连接、生成嵌入式系统的硬件、接口和算法的驱动,对CPU核、芯片集成接口、虚拟设备和纯算法进行了封装(该封装被称为“Embedded Beans”),并把这些功能变成属性、方法和事件,这与面向对象的程序设计方法是一样的。用户在进行程序设计时,通过调用Processor Expert提供的各种Bean,可以方便的对DSP内核、外部中断、DSP的片上外设及程序所需的各种通用算法进行设置.使用户只需关注整个设计的创造性部分,而不是花费大量时间让芯片正常工作,大大提高了生产率。本文的FIR滤波器的实现,就是基于Processor Expert的“DSP_Func_DFR”Bean和“DSP_MEM”Bean的。现将具体的设计过程描述如下:

进入CodeWarrior开发环境,选中菜单项“Processor Expertl| View| Bean Selector”,在弹出的“Bean Selector”窗口中,选中负责内存管理的“DSP_MEM”Bean和负责数字信号处理的“DSP_Func_DFR”Beafl加入工程文件,将“DSP_Func_DFR”Bean中的“dfrl6FIRCreate”、“dfrl6FIR”和“dfrl6FIRDestroy”方法加入主程序。修改主程序如下:

5 结束语

本文设计的 16阶线性相位 FIR数字低通滤波器,利用 56F8013芯片实现时,处理数据的系统时钟频率为 36MHz,采样速率为4MHz,计算结果和软件计算结果相比误差≤±1。在实际使用时,还可以根据不同要求,方便地对该 FIR滤波器进行修改以满足不同的指标要求。另外,在本文设计的低通滤波器基础上,可以通过简单地重组滤波器特性参数,得到高通或带通滤波器。同时 DSP器件的可编程特性,可方便地对电路进行改进,便于电路性能的进一步提高。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 模糊逻辑在 DSP 上实时执行2023/7/25 17:13:30

- 多速率DSP及其在数模转换中的应用2023/6/12 15:28:52

- 使用 DSP 加速 CORDIC 算法2023/3/29 15:46:30

- 高速DSP系统的信号完整性2022/9/26 16:45:38

- 自适应噪声消除系统的实现2022/1/17 17:51:17