|

摘 要: 介绍一种使用PCI宏核逻辑进行的更加简单高效的PCI口设计方法。该方法将PCI接口和PCI用户逻辑集成在一片FPGA里,可以对整个逻辑进行仿真调试,大大缩短了开发周期、提高了系统集成度和性能。重点叙述了ALTERA公司提供的32位TAGET接口宏核pci_t32的原理和结构,分析了时序设计要点,给出了典型应用的逻辑设计框图和注意事项。

关键词:PCI总线 接口 现场可编程逻辑阵列 仿真

|

|

1 PCI总线及其接口概述

PCI总线是高速同步总线,具有32bit总线宽度,工作频率是33MHz,传输率为132Mbyte/s,远远大于ISA总线5Mbyte/s的速率。PICMG(PCI工业计算机制造商联盟)制定的更加坚固耐用的Compact PCI总线规范,支持64位总线宽度,66MHz作频率,传输率为528Mbye/s。基于PC机的高速数据采集系统和各种虚拟仪器,几乎都选择了PCI总线。在现代高速通讯、测试等领域的嵌入式应用中,Compact PCI总线大有超过VME和VXI总线的趋势。PCI的高性能、高效率以及与现有标准的兼容性和充裕的发展潜力,是其它总线所不能及的,被计算机界公认为高瞻远瞩的局部总线标准。

PCI总线接口相对其它总线接口来说是比较复杂的,它不但有着严格的同步时序要求,而且为了实现即插即用和自动配置,PCI接口还必须有许多配置寄存器。根据用户设备的性质不同,PCI设备分为MASTER(主设备)和TARGET(从设备),因此PCI接口类型也就分为MASTER和TARGET两种接口。概括地说,PCI接口主要包括PCI标准配置寄存器(64字节)、PCI 总线逻辑接口、用户设备逻辑接口、数据缓冲区等。

作为一般应用设计工程师,为缩短开发周期,没有必要自己去设计全部的复杂的接口逻辑,甚至可以不必完全理解PCI规范的细节,就能进行PCI用户设备的设计。目前,市场上有一些专用PCI接口芯片,如AMCC公司的S5920(TARGET接口)、S5933(MASTER接口)等。使用这些专用PCI接口芯片,设计者只需要使用地址线、数据线以及少数几个读写控制信号,就能实现PCI总线与PCI用户设备之间的连接,类似ISA总线接口那么简单方便。

随着FPGA (现场可编程逻辑阵列请介绍一下Flash的全面管理问题。) 技术的快速发展,万门以上乃至几十万门逻辑阵列的使用越来越普遍,FPGA的单片价格也大幅度下降。与专用PCI接口芯片相似,很多FPGA制造商都提供了PCI接口宏核逻辑(PCI MegaCore)。设计者可以将PCI用户逻辑与PCI MegaCore集成在一片FPGA里,并且可以在顶层通过仿真来验证PCI接口以及用户逻辑设计的正确与否,这样可以大幅度提高调试速度,缩短开发周期,提高电路板的集成度和系统的性能。

ALTERA公司提供了多种不同功能的PCI MegaCore,例如:pci _a(带有DMA的32位MASTER/TARGET接口),pci_mt64(支持64位的MASTER/TARGET接口),pci_mt32(32位的MASTER/TARGET接口),pci_t64(支持64位的TARGET接口),pci_t32(32位的TARGET接口)等。不同的PCI MegaCore占用的资源是不同的,设计者可以根据PCI用户设备的需求来选择。

本文将介绍ALTERA公司提供的简单的32位PCI TARGET接口宏核逻辑pci_t32。重点介绍利用pci_t32进行PCI接口设计的方法及应用注意事项,并给出具体设计实例。其它PCI MegaCore的设计方法与此相类似。本文不介绍有关PCI规范的细节内容。

|

2 Pci_t32 MegaCore的内部结构及外围信号

Pci_t32是ALTERA公司提供的简单的32位PCI TARGET接口宏核逻辑,支持33MHz和66MHz的PCI时钟。

Pci_t32内部结构包含如下几个模块:

PCI总线配置寄存器,是符合PCI规范2.2版规定的所有配置寄存器。配置寄存器用于识别设备、控制PCI总线功能、提供PCI总线状态等。

奇偶校验模块,用于对数据、地址、命令等进行奇偶校验。

PCI侧TARGET控制模块(PCI target control block),用于控制pci_t32(作为TARGET)与PCI总线的各种操作。

用户设备侧TARGET控制模块(local target control block),用于控制pci_t32(作为TARGET)与用户逻辑的各种操作。

用户设备侧地址/数据/命令/字节使能模块,接收和输出用户侧的所有地址/数据/命令/字节使能等信号。

Pci_t32内部功能模块及周边信号如图1所示。 |

|

|

|

左侧PCI信号是符合PCI规范的标准信号,在这里不多加解释。下面重点介绍右侧用户逻辑接口local信号:

L_aci 31 0 ,local侧地址、数据输入信号。

L_cbeni 3 0 ,local侧命令、字节使能输入信号,位定义及时序符合PCI规范。

L_dato 31 0 ,local侧数据输出信号。

L_adro 31 0 ,local侧地址输出信号。

L_beno 30 ,local侧字节使能输出信号,位定义及时序符合PCI规范。

L_cmdo30,local侧命令输出信号,位定义及时序符合PCI规范。

Lt_rdyn,local侧目标设备准备好信号(target ready),对pci_t32是输入信号。

Lt_discn,local侧目标设备通过置低该信号请求pci_t32向PCI 侧主设备发出断开连接信号(disconnect request),对pci_t32是输入信号。

Lt_abortn,local侧目标设备通过置低该信号来请求pci_t32向PCI 侧主设备发出放弃操作信号,对pci_t32是输入信号。

Lt_irqn,local侧目标设备中断请求信号,对pci_t32是输入信号。

Lt_framen,PCI主设备通过pci_t32读写local侧目标设备时,pci_t32置低该信号(输出信号).

Lt_ackn,当为目标写操作时,PCI_t32置低该信号(输出信号),表示数据有效;当为目标读操作时,PCI_t32置低该信号(输出信号),表示已准备好读数。

Lt_dxfrn,输出信号,表示local 目标设备数据传输成功。

Lt_tsr 11 0,输出信号,控制local目标设备状态寄存器。

Cmd_reg 5 0,配置命令寄存器输出信号。Bit0,I/O操作使能;bit1,Memory操作使能;bit2,保留;bit3,memory写无效使能;bit4,奇偶校验出错响应使能;bit5,系统出错响应使能。

Stat_reg 5 0 ,配置状态寄存器输出信号。

|

3 读写操作时序分析与设计要点

pci规范中定义了两种读写操作,即Memory和I/O的读写。Pci_t32的读写操作包括:32位的Memory单周期读写、Memory猝发读写、I/O单周期读写以及配置读写。Pci_t32 的Memory读写分为单周期和猝发两种模式,而I/O的读写只有单周期模式。所谓猝发模式,即在给出首地址后,主设备连续读写多个数据,用户设备应能对首地址自动加1。配置读写是指pci主设备对pci_t32的配置空间寄存器进行读写操作,pci主设备与pci_t32之间的接口是无缝连接。本文只分析32位Memory单周期读写时序,其它模式的读写时序大同小异,此略。

3.1 Memory 读操作

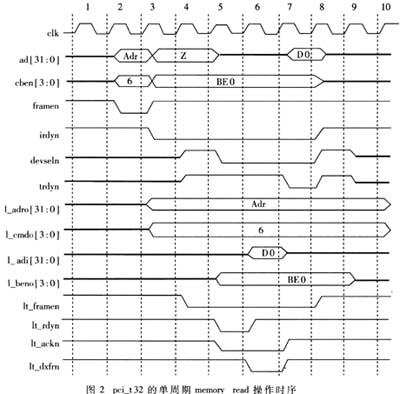

pci_t32的单周期memory read操作时序如图2所示。 |

|

|

时序分析及用户逻辑设计要点:pci主设备在第2个clk给出要读的目标地址ad 31 0 和Memory读命令cben 3 0 =6,pci_t32在第3个clk向用户设备给出读目标地址1_adro 31 0和Memory读命令l_cmdo 3 0 =6。用户设备要对l_cmdo 3 0 译码来判断是何种操作,对l_adro 31 0 译码来选择目标地址。在lt_framen输出为低的下个时钟周期,若用户设备逻辑准备好要输出的数据,可以置低lt_rdyn。若用户逻辑没有准备好,可以延迟置低lt_rdyn来产生延时等待周期。当lt_dxfrn输出为低电平时(第6个clk),pci用户设备必须将目标地址的数据D0放到l_adi 31 0 ,用户逻辑可以用lt_dxfrn来作为存储单元的输出使能信号(/Output Enable)。这样,在第7个clk的上升沿pci_t32可以采样到数据D0。在第8个clk的上升沿pci主设备可以得到数据D0。

3.2 Memory写操作

pci_t32的单周期memory 写操作时序如图3所示。 |

|

|

|

时序分析及用户逻辑设计要点:pci主设备在第2个clk给出要写的目标地址ad 31 0 和Memory写命令cben 3 0 =7,pci_t32在第3个clk向用户设备给出写目标地址l_adro 31 0 和Memory写命令l_cmdo 3 0 =7。用户设备要对l_cmdo 3 0 译码来判断是何种操作,对l_adro 31 0 译码来选择目标地址。在lt_framen输出为低的下个时钟周期,若用户设备逻辑准备好接收pci_32t写的数据,可以置低lt_rdyn。若用户逻辑没有准备好,可以延迟置低lt_rdyn来产生延时等待周期。当lt_dxfrn输出为低电平时(第7个clk),pci_t32已经将输出的有效数据放在l_dato 31 0 上,pci用户设备必须在第8个clk的上升沿将l_dato 31 0 输出的数据D0锁存至目标地址l_adro 31 0 ,用户设备逻辑可以用第8个clk的上升沿来作为锁存器的锁存时钟,用lt_dxfrn作为锁存器的锁存使能信号(/Latch Enable)或存储单元的写使能信号(/Write Enable)。

|

4 应用设计实例及注意事项

笔者已经成功地将pci_t32用于一个compact PCI的TARGET控制模块中。在这个模块中,主设备Master通过pci_t32来读写64个32bit控制寄存器,再由这些寄存器组去控制外部设备。在本系统的FPGA里,还有仲裁器等其它逻辑,PCI时钟是33MHz,芯片选用的是EPF10K100EQC240-2。系统逻辑设计的框架如图4所示。 |

|

|

|

在寄存器组里还有一些简单的选通、三态控制等逻辑,此略。L_adro 6 0 译码选择寄存器组里的目标寄存器。当/WE有效时,l_dato 31 0 上是pci_t32输出的有效数据;当/OE有效时,寄存器组必须将要输出的数据放到l_adi 31 0 总线上。

在使用pci_t32时,还有一些值得注意的地方,如下所述:

1 用户逻辑的时钟(本系统的寄存器组的时钟clk)与进入pci_t32的时钟必须是同一个时钟,并且在定义管脚时应选用全局时钟线(global clock)。这样,可以保证时钟的同步,提高系统的性能。

2 从库中调出pci_t32.gdf的symbol,在其右上角,可以看到一些默认设置,双击这些参数,可以改变设置。包括:DEVICE_ID、REVISION_ID、CLASS_CODE、VENDOR_ID、基地址等PCI标准配置寄存器。

3 选择芯片主要考虑两个因素:

容量和速度。芯片容量包括片内的逻辑单元和可用I/O管脚数。芯片速度主要由PCI系统工作的时钟频率以及用户逻辑的大小和优化程度两方面决定。

Pci_t32的资源占用较小,在用EPF10K100EFC484-1芯片编译时,占用621个LC(Logic Cell)。而PCI宏核pci_a,在用EPF10K100EFC484-1芯片编译时,占用923个LC。EPF10K100共有约5000个LC。

Altera的FPGA有多种容量和速度级,一般来说,-1速度级的芯片可以满足66MHz时钟的PCI时序要求,-2速度级的芯片只能满足33MHz时钟的PCI时序要求。

速度和容量是否能满足用户的要求,必须要进行仿真才能终确定。

现在FPGA的价格日渐下降,大容量的FPGA使用越来越普遍。各家芯片供应商都提供了各种 PCI宏核逻辑。设计者可以将PCI用户逻辑与PCI接口宏核逻辑集成在一片FPGA里,在顶层通过仿真来验证PCI接口以及用户逻辑设计的正确与否。这样,可以大幅度提高调试速度,缩短开发周期,提高电路板的集成度和系统性能。可以肯定地预言,使用PCI接口宏核逻辑来进行PCI接口设计是今后设计PCI接口的主要方法。PCI接口宏核逻辑将会受到越来越多的设计工程师的青睐。

|

|

参考文献

1 ALTERA Device Data book 1999.ALTERA,1999

2 PCI MegaCore Function User Guider,Version 1.0.ALTERA,1999年12月

3 金 革.可编程逻辑阵列FPGA和EPLD.合肥:中国科技大学出版社,1996

4 PCI datasheet https://www.dzsc.com/datasheet/PCI_1201469.html.

5 Memory datasheet https://www.dzsc.com/datasheet/Memory_1082507.html.

6 EPF10K100EFC484-1 datasheet https://www.dzsc.com/datasheet/EPF10K100EFC484-1_2527956.html.

7 EPF10K100 datasheet https://www.dzsc.com/datasheet/EPF10K100_300894.html.

|

关键词:基于FPGA的PCI接口设计EPF10K100EFC484-1EPF10K100EQC240-2S5933S5920EPF10K100