基于CMSIS标准的Cortex-M3应用软件开发

出处:shenqzh 发布于:2009-12-21 14:28:25

引 言

ARM公司于2008年11月12日发布了ARM Cortex微控制器软件接口标准(CMSIS:Cortex Microcon-troller Software Interface Standard)。CMSIS是独立于供应商的Cortex-M处理器系列硬件抽象层,为芯片厂商和中间件供应商提供了连续的、简单的处理器软件接口,简化了软件复用,降低了Cortex-M3上操作系统的移植难度,并缩短了新入门的微控制器开发者的学习时间和新产品的上市时间。

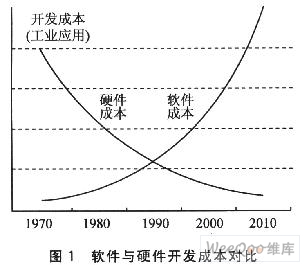

根据近期的调查研究,软件开发已经被嵌入式行业公认为主要的开发成本。图1为近年来软件开发与硬件开发成本对比图。因此,ARM与Atmel、IAR、Keil、hami-nary Micro、Micrium、NXP、SEGGER和ST等诸多芯片和软件厂商合作,将所有Cortex芯片厂商产品的软件接口标准化,制定了CMSIS标准。此举意在降低软件开发成本,尤其针对新设备项目开发,或者将已有软件移植到其他芯片厂商提供的基于Cortex处理器的微控制器的情况。有了该标准,芯片厂商就能够将他们的资源专注于产品外设特性的差异化,并且消除对微控制器进行编程时需要维持的不同的、互相不兼容的标准的需求,从而达到降低开发成本的目的。

1 基于CMSIS标准的软件架构

如图2所示,基于CMSIS标准的软件架构主要分为以下4层:用户应用层、操作系统及中间件接口层、CMSIS层、硬件寄存器层。其中CMSIS层起着承上启下的作用:一方面该层对硬件寄存器层进行统一实现,屏蔽了不同厂商对Cortex-M系列微处理器核内外设寄存器的不同定义;另一方面又向上层的操作系统及中间件接口层和应用层提供接口,简化了应用程序开发难度,使开发人员能够在完全透明的情况下进行应用程序开发。也正是如此,CMSIS层的实现相对复杂。

CMSIS层主要分为3部分。

①核内外设访问层(CPAL):由ARM负责实现。包括对寄存器地址的定义,对核寄存器、NVIC、调试子系统的访问接口定义以及对特殊用途寄存器的访问接口(如CONTROL和xPSR)定义。由于对特殊寄存器的访问以内联方式定义,所以ARM针对不同的编译器统一用_INLINE来屏蔽差异。该层定义的接口函数均是可重入的。

②中间件访问层(MWAL):由ARM负责实现,但芯片厂商需要针对所生产的设备特性对该层进行更新。该层主要负责定义一些中间件访问的API函数,例如为TCP/IP协议栈、SD/MMC、USB协议以及实时操作系统的访问与调试提供标准软件接口。该层在1.1标准中尚未实现。

③设备外设访问层(DPAL):由芯片厂商负责实现。该层的实现与CPAL类似,负责对硬件寄存器地址以及外设访问接口进行定义。该层可调用CPAL层提供的接口函数,同时根据设备特性对异常向量表进行扩展,以处理相应外设的中断请求。

2 CMSIS规范

(1)文件结构

CMSIS的文件结构如图3所示(以STM32为例)。其中stdint.h包括对8位、16位、32位等类型指示符的定义,主要用来屏蔽不同编译器之前的差异。core_cm3.h和core_cm3.C中包括Cortex_M3核的全局变量声明和定义,并定义一些静态功能函数。system_

(2)工具链

CMSIS支持目前嵌入式开发的三大主流工具链,即ARM ReakView(armcc)、IAR EWARM(iccarm)以及GNU工具链(gcc)。通过在core_cm3.C中的如下定义,来屏蔽一些编译器内置关键字的差异。

这样,CPAL中的功能函数就可以被定义成静态内联类型(static_INLINE),实现编译优化。

(3)中断异常

CMSIS对异常和中断标识符、中断处理函数名以及中断向量异常号都有严格的要求。异常和中断标识符需加后缀_IRQn,系统异常向量号必须为负值,而设备的中断向量号是从0开始递增,具体的定义如下所示(以STM32为例):

CMSIS对系统异常处理函数以及普通的中断处理函数名的定义也有所不同。系统异常处理函数名需加后缀_Handler,而普通中断处理函数名则加后缀_IRQHandler。这些异常中断处理函数被定义为weak属性,以便在其他的文件中重新实现时不出现重复定义的错误。这些处理函数的地址用来填充中断异常向量表,并在启动代码中给以声明,例如:NMI_Handler、MemManage_Handler、SysTick_Handler、WWDG_IRQHandler等。

(4)数据类型

CMSIS对数据类型的定义是在stdint.h中完成的,对核寄存器结构体的定义是在core_cm3.h中完成的,寄存器的访问权限是通过相应的标识来指示的。CMSIS定义以下3种标识符来指定访问权限:_I(volatile const)、_O(volatile)和_IO(volatile)。其中_I用来指定只读权限,_O指定只写权限,_IO指定读写权限。

(5)调 试

嵌入式软件开发中的一个基本需求就是能通过终端来输出调试信息,一般可通过2种方式实现:一种是使用串口线连接板上的UART和PC上的COM口,通过PC上的超级终端来查看调试信息;另一种则是采用半主机机制,但有可能不被所用的工具链支持。基于Cortex-M3核的软件调试突破了这样的限制,Cortex-M3内核提供了一个ITM(Instrumentation Trace Macrocell)接口,通过SWV(Serial Wire Viewer)可调试由SWO引脚接收到的ITM数据。ITM实现了32个通用的数据通道,基于这样的实现,CMSIS规定用通道0作为终端来输出调试信息,通道31用于操作系统的输出调试(特权模式访问)。在core_cm3.h中定义了ITM_SendChar()函数,因此可通过调用该函数来重写fputc,以在应用程序中通过printf打印调试信息,并可通过ITM Viewer查看这些调试信息。有了这样的实现,嵌入式软件开发者就可以在不配置串口和使用终端调试软件的情况下输出调试信息,在一定程度上减少了工作量。

(6)安全机制

在嵌入式软件开发过程中,代码的安全性和健壮性一直是开发人员所关注的,因此CMSIS在这方面也作出了努力,所有的CMSIS代码都基于MISRA-C2004(Motor Industry Software Reliability Association forthe C programming language)标准。MIRSA-C 2004制定了一系列安全机制用来保证驱动层软件的安全性,是嵌入式行业都应遵循的标准。对于不符合MISRA标准的,编译器会提示错误或警告,这主要取决于开发者所使用的工具链。

3 基于CMSIS标准的代码实现

CMSIS降低了代码开发的难度,为了更好地诠释这一点,下面以一个基于STM32微处理器的简单例子来说明。代码实现如下:

可以看到用户程序中仅需短短的几行代码就实现了定时器的功能,每隔1 S报数1次,并可通过ITM窗口查看输出的调试信息。其中SystemInit()用来初始化时钟,SysTick_Config()用来配置系统定时器,而SysTick_Han-dler()用来处理系统时钟异常,该异常每1 ms发生1次。由于重写了fputc(),所以可通过printf()函数将调试信息打印到ITM窗口上,输出结果如图4所示。

结 语

本文阐述了基于CMSIS标准的软件架构、规范,并通过一个实例更加清晰地解读了CMSIS作为一个新的基于Cortex-M核处理器系列的软件开发标准所具有的巨大潜力。它不仅降低了软件开发的难度,更减少了软件开发的成本。因此,工程师尽早掌握CMSIS标准,对进行基于Cortex-M3处理器的软件开发会大有帮助。

参考文献:

[1]. COM datasheet https://www.dzsc.com/datasheet/COM_1118194.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 深入解析嵌入式 OPENAMP 框架:开启异核通信新时代2025/7/22 16:27:29

- 一文快速了解OPENWRT基础知识2025/7/14 16:59:04

- 独立 ADC 优势大揭秘:为何不可替代?2025/7/7 16:21:04

- 深入剖析:嵌入式中 RS485、RS422 和 RS232 的特点差异2025/7/5 15:07:54

- 揭秘嵌入式 MCU:浮点数据处理难点及应对策略2025/6/20 15:19:07