基于LAN91C111的嵌入式以太网接口设计

出处:wanhuikfb 发布于:2011-03-03 11:26:09

随着CPU性能的大幅度提升, 嵌入式系统的设计已经进入了更广泛的领域。随着FPGA的不断发展和规模的进一步强大, SOPC的应用也越来越广泛。由于SOPC的可编程特性很受嵌入式系统开发人员的青睐, 因此, 随着信息产业和微电子技术的发展, 可编程嵌入式系统设计已经成为信息产业热门的技术之一, FPGA正以各种电子产品的形式进入人们日常生活的各个角落。

以太网以其良好的通用性和带宽性能成为新一代工业控制网络的焦点, 目前, 关于嵌入式以太网的设计方案大部分是基于单片机的。由于单片机的速度慢, 而FPGA作为一种特殊的嵌入式微处理器系统, 则具有快速处理数据的能力。因此, 在嵌入式网络设备中引入FPGA技术, 可以使嵌入式以太网的速度更快。为此, 本文介绍基于FPGA 的嵌入式系统与LAN91C111 型自适应10Mb/100Mb嵌入式以太网的接口电路与实现方法。

1 硬件设计

1.1 FPGA的特点

本系统的主控芯片采用ALTERA公司CycloneII系列的EP2C35F484。FPGA内部集成有锁相环,可以把外部时钟倍频, 其频率可以到几百兆, 同时具有丰富的IO资源, 可以方便连接外设。FPGA的并行执行程序方式具有处理更复杂功能的能力, 而且内部嵌有SOPC和DSP。可编程SOPC是一种特殊的嵌入式系统, 具有灵活的设计方式, 而且可裁剪、可扩充, 同时软硬件在系统可编程功能。

1.2 嵌入式以太网控制器LAN91C111

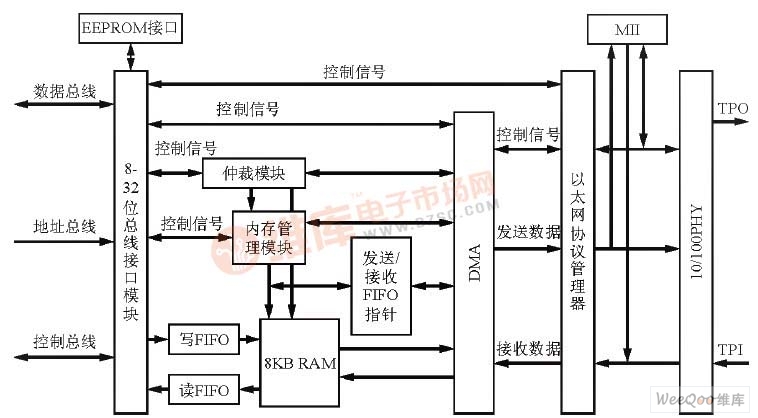

以太网控制芯片所选用的SMSC 公司LAN91C111芯片是专门用于嵌入式产品的10M/100M第三代快速以太网控制器。该器件具有可编程、CRC校验、同步或异步工作方式, 且具有低功耗CMOS设计和小尺寸等特点, 是设计嵌入式以太网网络接口的良好选择。LAN91C111的原理框图如图1所示。

图1 LAN91C111的原理框图

LAN91C111集成了CSMA/CD (带碰撞的载波侦听多路接入) 协议的MAC (媒体层) 和PHY (物理层)。其主要特点是支持IEEE802.3/802 U以太网标准、自适应10M/100M, 全双工/半双工收发方式、有8KB的片上FIFO存储器、支持8位或16位或32位总线方式、支持先进的传输队列管理、有串行EEPROM选择性配置口、并支持突发数据传输、支持全双工交换式以太网、增强式能量管理功能和低功耗的CMOS设计。

总线接口模块是由数据总线、地址总线、控制总线以8位、16位、或32位形式与外部数据进行交互。LAN91C111以太网控制器遵循IEEE颁布的802.3 以太网传输协议, 内部集成有8KB 的RAM, 可通过内部的内存管理模块、仲裁模块和DMA共同管理数据包的发送与接收。其仲裁器监视以太网总线的数据交流, 一旦发生阻塞, 仲裁器一方面通过总线接口单元与外部CPU联系; 一方面控制内存控制单元, 实现总线的数据协调。

LAN91C111内部的RAM可以缓存数据, 在全双工工作模式下, 数据传输速率可达到10M/100Mbps。

所有内部寄存器的初始值均放在EEPROM中, 自举时可完成自动初始化。在数据传输过程中, 若以10Mbps速率传输, 则可采用Manchester编码,并以两层曼彻斯特代替三电平, 且没有扰频器和解扰频器; 若以100Mbps速率传输, 则先将发送到RAM中的数据包以包号的形式存放在FIFO的发送队列中, 然后按照规则逐个将数据包发送到PHY模块进行4B-5B编码, 发送数据端可将通过扰频器整理后的4B-5B数据包变换成MLT-3后输出。而在接收时, 则将数据包复制并发送到解扰频器进行整理, 然后再发送到4B-5B解码器进行解码。

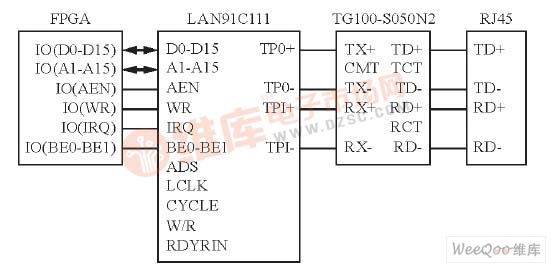

1.3 硬件连接

本设计在FPGA芯片EP2C35中嵌入了32位的NIOS II处理器。由于LAN91C111是专为嵌入式系统设计的, 因而其外围电路相对比较简单。图2所示是其硬件连接图, 图中的地址线、数据线、控制线分别与FPGA相连。由于采用的是16位数据传输方式, 因此只用到数据总线的低16位。控制线中的AEN为片选信号, INTR0为外部中断信号, WR为读写信号, BE0-BE1为字节选择端。

LAN91C111 中的ADS、LCLK、CYCLE、W/R、RDYRTN 信号应均加一个1kΩ 的上拉电阻。

TG100-S050N2是以太网的变压滤波器。TX+ 、TX- 、RX+ 、RX- 分别与LAN91C111 的TPO+ 、TPO-、TPI+、YPI-相连。TG100-S050N2的CMT端也应接一个1kΩ的上拉电阻。RJ45 的TD+ 、TD-、RD+、RD-分别与TG100-S050N2的TD+、TD-、RD+、RD-相连。在TG100-S050N2的TCT和RCT亦应分别接一个75Ω的电阻和1nF的滤波电容。这样即可在控制线的作用下完成FPGA与LAN91C111之间的数据通信。

图2 系统硬件连接图

2 软件设计

ALTERA公司提供的硬件抽象层(HAL) 中封装了系统中硬件的相关细节和驱动程序, 用户可在HAL的基础上方便地开发存储等应用程序。

NIOS II IDE环境中集成有μCOS II和LWIP, 其中LWIP必须在μCOS的支持下使用。μC/OS II是一种公开源代码, 结构小巧, 而且具有可剥夺实时内核的操作系统, 它可移植、可裁剪, 多可管理64个任务, 其每个任务都拥有自己独立的堆栈, 大部分源码可使用ANSI C语言编写, 整个软件部分可在NIOS II IDE开发环境下完成。由于程序的内容较多, 本文着重介绍LAN91C111的初始化、发送数据、接收数据三个部分的软件设计方法。

2.1 初始化

ALTERA提供有LWIP的NIOS II 端口, 其源代码包含在NIOS II 开发工具包中。LWIP可为NIOS II处理器提供对以太网连接栈的快速、开源地访问。ALTERA的LWIP端口包括套接字API封装, 提供有标准的、文档说明齐全的套接字API。LWIP协议栈的主要接口是标准的套接字接口。除了套接字接口以外, 还可调用lwip_stack_init ()函数和lwip_devices_init () 函数来对堆栈和驱动程序初始化。通过HAL 系统代码可调用init_done_func ()、get_mac_addr () 和get_ip_addr() 函数来设置MAC地址和IP地址。为了初始化堆栈, 在调用OSStart启动μC/OS II 调度程序之前应调用函数lwip_stack_init ( ) , 其原型为voidlwip_stack_init ( int thread_prio, void(*init_done_func) (void*), void *arg)。堆栈初始化后, 还必须调用函数init_done_func (), 而该函数必须调用函数lwip_devices_init () 。利用函数lwip_devices_init () 可以对在system.h中定义的所有已安装的以太网设备驱动程序进行注册, 若返回一个非0值则表示注册成功。注册成功后,TCP/IP栈即可使用, 之后便可在程序中创建任务。该函数的参数是接收线程的优先级。LWIP系统码在设备初始化过程中, 可通过lwip_devices_init ( ) 函数调用函数get_mac_addr ( ) 和get_ip_addr ()。用户通过编写这些函数, 可在系统中将MAC和IP地址存放在任意位置, 从而代替在设备驱动程序中固定位置的硬编码, 并增加系统的灵活性。设计时, 可以将MAC地址存放在Flash存储器中, 也可以将MAC地址存放在片上内嵌的存储器中。当所有的初始化都准备好后即可调用OSStart () 以启动RTOS进行任务调度。这个过程需要设置以太网目的地址、以太网源地址、协议类型, 然后再按照所设置的协议类型来设置数据包。

2.2 数据的发送和接收

数据的接收和发送可采用中断方式。中断服务程序通过检查LAN91C111的中断状态寄存器来判断是发送中断请求还是接收中断请求。初始化完成后, 即可创建任务, 建立套接字, 绑定端口, 绑定完之后, 再*端口。当LAN91C111接收到数据包时, 可由EPH模块察看此数据包的目的地址, 若为本网卡的MAC地址或广播地址或多播地址, 则把此数据包传送到LAN91C111的RAM中, 并向处理器发送中断, 由处理器进行数据处理。由于采用的是TCP/IP协议, 接收数据应调用read () 函数来接收建立连接的套接字中的数据,并将其放入缓冲区。发送过程则是由FPGA将数据传送到LAN91C111, 再由LAN91C111将接收到的数据封装成数据包, 并检测网络, 当没有数据传输时, 再将数据包传输到网络中, 并向处理器发送中断信号, 以表示数据传送完毕。发送数据时通过调用write () 函数可将要发送的数据发送到指定连接的目的地址。

3 结束语

本文的整个设计使用了逻辑单元(LE) 5314个, 占用EP2C35F484芯片内部资源的16%, 这充分体现了FPGA资源的丰富性。在传统设计中,通常选用单片机和低速网卡的设计方案, 这在实际应用中, 网络速度相对较慢, 而本设计中选用高速的以太网控制芯片LAN91C111和高速的FPGA,极大地提高了系统的网络数据处理能力,并可满足网络数据采集的需求。另外, 基于FPGA的NIOS II方案, 还可根据实际需要添加不同IP, 这也体现了SOPC的灵活性与可裁减性。

参考文献:

[1]. LAN91C111 datasheet https://www.dzsc.com/datasheet/LAN91C111+_1054180.html.

[2]. EP2C35 datasheet https://www.dzsc.com/datasheet/EP2C35_1438348.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- iic通信协议是什么2024/4/30 17:15:26

- 差分传输中的共模噪声:特征和原因2024/4/25 16:15:44

- 毫米波通信技术之香农和香农定理2024/4/24 17:40:43

- 网桥是什么_网桥如何设置2024/4/12 17:39:56

- TEC 控制器在电信系统中的应用指南2024/4/8 17:43:07