FPGA处理器在数字光端机系统中的应用

出处:xzl 发布于:2011-08-26 10:00:33

由于数字技术与传统的模拟技术相比在很多方面都具有明显的优势,所以正如数字技术在许多领域取代了模拟技术一样,光端机的数字化也是一种必然趋势。目前,数字视频光端机主要有两种技术方式:一种是MPEG II图象压缩数字光端机,另一种是全数字非压缩视频光端机。图象压缩数字光端机一般采用MPEG II图象压缩技术,它能将活动图象压缩成N×2Mbps的数据流通过标准电信通信接口传输或者直接通过光纤传输。由于采用了图象压缩技术,它能大大降低信号传输带宽。

全数字非压缩视频光端机采用全数字无压缩技术,因此能支持任何高分辨率运动、静止图像无失真传输;克服了常规的模拟调频、调相、调幅光端机多路信号同时传输时交调干扰严重、容易受环境干扰影响、传输质量低劣、长期工作稳定性不高等缺点。并且支持音频双向、数据双向、开关量双向、以太网、电话等信号的并行传输,现场接线方便,即插即用。

系统框架与工作原理

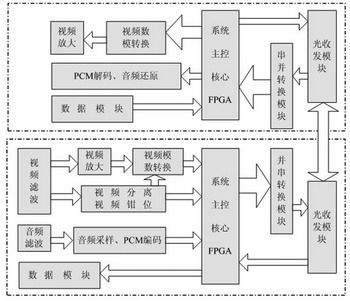

整个系统由控制模块FPGA、音频采样编解码模块、视频分离模块、视频放大模块、视频A/D和D/A转换模块、并串/串并转换模块、光纤调制收发模块、电源控制模块和485数据传输模块。图1是该系统的系统框图。

图1 系统结构框图

系统的工作原理为:光端机系统分为两部分,分别为:发射机和接收机。在发射端,来自监视器或其他视频源的视频信号首先经过发射板上的视频滤波网络去除噪声干扰信号,然后对该视频信号进行视频分离和视频放大。视频分离模块得到视频信号的行、场同步信号以及奇偶场信号、视频钳位等重要的视频信息。接下来,对放大后的视频信号进行A/D转换,得到的数字化的视频信号送入系统主控FPGA中。与此同时,如果系统检测到了有音频信号的存在,则对其进行音频滤波、音频数字化采样以及音频PCM编码。经过PCM编码后的音频信号,送入系统主控FPGA中。反向数据传输主要是485信号,该信号也送入到FPGA.这样,系统主控FPGA对来自不同模块的视频、音频、数据等信号整合,时分复用地将各个信号编码成8位并行信号流送入到并串转换模块。信号流经过并串转换后变成高速的LVDS信号驱动光纤收发模块以波分复用的方式完成了电/光变化和光发射。在光端机的接收端,经过以上的逆过程,完成对原始信号的恢复。

系统硬件组成

1 FPGA控制器

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,而且消耗更多的电能。但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。厂商也可能会提供便宜的但是编辑能力差的FPGA.因为这些芯片有比较差的可编辑能力,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于ASIC的芯片上。另外一种方法是用CPLD(复杂可编程逻辑器件备)。

系统的控制部分是整个系统的心脏,为了满足对高速、多路数据流的实时处理,要求系统控制器必须有较高的工作频率和反应能力。其次,对于系统时分复用部分,为了信号的同步化,需要系统控制器内嵌RAM和FIFO等功能块。此外,同时作为嵌入式系统,处理器必须有着低功耗的要求。目前,FPGA处理器已经遍及工业控制、消费电子产品、通信系统等各类产品市场。按照低成本、低功耗、小体积、多功能及较为强大的数据处理能力,Altera公司CycloneII系列的EP1C3144是一个非常好的选择。

图2 视频分离硬件电路

2 视频分离模块

视频信号中除了包含图像信号之外,还包括了行同步信号、行消隐信号、场同步信号、场消隐信号以及槽脉冲信号、前均衡脉冲、后均衡脉冲等,因此,若要对视频信号进行采集,就必须准确地把握各种信号间的逻辑关系。LM1881就是针对视频信号的同步分离而生产的,它为视频信号的处理提供了极大的方便。此处电路设计如图2所示。

LM1881可以从0.5~2V的标准负极性NTSC制、PAL制、SECAM制视频信号中提取复合同步场同步、奇偶场识别等信号,这些信号都是图像数字采集所需要的同步信号,有了它们,便可确定采集点在哪一场,哪一行。LM1881也能对非标准的视频信号进行同步分离,通过固定的时间延迟产生默认的输出作为场同步输出。

图3 A/D转换硬件电路

3 A/D和D/A转换模块

随着数字技术,特别是信息技术的飞速发展与普及,在现代控制、通信及检测等领域,为了提高系统的性能指标,对信号的处理广泛采用了数字计算机技术。由于系统的实际对象往往都是一些模拟量(如温度、压力、位移、图像等),要使计算机或数字仪表能识别、处理这些信号,必须首先将这些模拟信号转换成数字信号;而经计算机分析、处理后输出的数字量也往往需要将其转换为相应模拟信号才能为执行机构所接受。这样,就需要一种能在模拟信号与数字信号之间起桥梁作用的电路--模数和数模转换器。

将模拟信号转换成数字信号的电路,称为模数转换器(简称A/D转换器或ADC,Analog to Digital Converter);将数字信号转换为模拟信号的电路称为数模转换器(简称D/A转换器或DAC,Digital to Analog Converter);A/D转换器和D/A转换器已成为信息系统中不可缺少的接口电路。

此处的A/D转换电路主要用来对视频滤波,放大后的视频信号进行数字化变换。电视图像信号的带宽理论计算值为7.37MHz,实际取5.5275MHz.由香农定理知,ADC的采样频率应该大于2倍的图像频率,所以ADC采用ADI公司的AD9280,工作频率为32MHz.该ADC具有良好的差分非线性度、模拟输入超出转换量程提示、内建自流电平回复和可调片内电压基准源等优势。

此处A/D转换电路设计如图3所示。

接收端A/D转换电路主要完成对数字化后的视频信号的模拟变换,还原出标准的视频信号。此处选用的DAC为ADI公司的高速AD9708.

AD9708采用+3V或+5V单电源供电,两路电流输出,转换速率高达125MHz,建立时间不大于35ns,转换为1/4 LSB.在+5V电源供电的情况下,其功耗为175mW;在+3V电源供电的情况下,其功耗为45mW.

为了特殊的需要,AD9708还兼容8位、10位和12位并行数据输入。当AD9708被设置成8位数据输入时,只要把管脚1设为输入有效数据位(MSB),管脚8设为输入有效数据位(LSB)即可。引脚1(DB13):输入有效数据位;引脚2~13(DB12~DB1):数据输入端;引脚14(DB0):输入有效。

4 并串/串并模块

低压差分信号是由ANSI/TIA/EIA-644-1995定义的用于高速数据传输的物理层接口标准(LVDS)。它具有超高速(速率可达1.4Gb/s)、超低功耗和低电磁辐射等特性,因而是在铜介质上实现千兆位速率通信的优选方案。而总线形低压差分信号LVDS是LVDS技术在多点通信领域的扩展,它要求有更大的驱动电流(10mA)和更好的阻抗匹配设计。

SN65LV1023和SN65LV1224是TI公司推出的10位总线型低压差分信号的应用芯片组。其中SN65LV1023是可将10位并行CMOS或TTL数据转换为具有内嵌时钟的高速串行差分数据流的串化器;而SN65LV1224则是接收该差分数据流并将它们转换为并行数据的解串器,它同时又可以重建并行时钟。采用该器件组进行数据串化时采用的是内嵌时钟,这样可有效地解决由于时钟与数据的不严格同步而制约高速传输的瓶颈问题。此处的硬件电路设计如图4所示。

图4 并串转化硬件示意图

系统软件设计

系统软件主要是对系统控制的FPGA的编程。整个程序基于模块化、结构化的软件开发思想编写。所用的开发工具是Altera公司出品的FPGA集成开发环境QuartusII,开发语言采用当今比较流行的大规模集成电路Verilog开发语言。

系统软件功能实现了A/D控制模块、语音编码控制模块、并串转换控制模块、串并转换控制模块、D/A控制模块、语音解码控制模块和反向数据的收发控制模块。

1 A/D控制模块

A/D控制模块以FPGA为主控,为AD9280提供采样时钟;同时采集AD9280A/D转换后的数字量。

FPGA系统时钟频率为32MHz,对于AD9280的采样时钟为16MHz,对系统时钟进行二分频后提供给AD9280.同时,在分频后的输出时钟的上升沿对A/D转换的结果进行读取,读取的结果存入FPGA中进行下一步应用。程序如下所示。

module AdControl(clk_in,reset,ad_data,clk_out,data_reg);

input clk_in,reset;

input [0:7]ad_data;

output clk_out;

output [0:7]data_reg;

reg [0:7]data_reg;

reg clk_out;

always@(posedgeclk_in)

begin

if(reset)

clk_out<=0;

else

clk_out<="clk_out;

end

always@(posedgeclk_out)

begin

data_reg<=ad_data;

end

endmodule

其中,clk_in为FPGA系统输入时钟;clk_out为分频后提供给ADC的采样时钟;reset为复位端,高电平复位;ad_data是A/D转换后得到的数字量;data_reg

用来存储A/D转换后的数字量。

2 语音编码控制模块

语音编码控制模块主要完成对PCM编码芯片提供数据编码时钟、数据使能控制以及编码后的数据接收。

此处程序如下所示。

module PcmControl(clk_in,reset,tdd,tdc,tde,pcm_data);

……

always@(posedgeclk_in)

begin

if(reset)

begintdc<=0; end

elsebegin

if(cnt0==7)

begin

tdc<="tdc;

cnt0<=0;

end

else

cnt0<=cnt0+1;

end

end

always@(posedgetdc)

begin

if(cnt1==140)

begin

tde<="tde;

cnt1<=0;

end

else

cnt1<=cnt1+1;

end

always@(posedgetdc)

begin

pcm_data<=tdd;

end

endmodule

其中,clk_in是FPGA系统时钟,reset为系统复位信号。信号tdd是PCM编码芯片的输出;信号pcm_data用来存放PCM编码数据;信号tdc是PCM编码时钟信号;信号tde是PCM编码使能时钟。

3 并串转换控制模块

系统主控FPGA对数字化的视频、语音信号进行时分复用后,将视频语音混合信号送给并串转换器。并串转换模块主要实现对并串转换器的时序控制,使能控制和数据输入控制。此处的部分程序如下所示。

moduleSnControl (clk_in,fpga_data,sn_clk,sn_data,sncontrol);

input clk_in;

input [0:9]fpga_data;

output [0:9]sn_data;

output sn_clk,sncontrol;

reg sn_clk,sncontrol;

reg [0:9]sn_data;

always@(posedgeclk_in)

begin

sn_clk<="sn_clk;

end

always

begin

sncontrol<=1;

end

always@(posedgesn_clk)

begin

sn_data<=fpga_data;

end

endmodule

其中,clk_in是FPGA系统时钟,信号sn_clk是并串转换器的转换时钟;信号fpga_data是FPGA对视频、语音时分复用编码后的数据;信号sn_data是并串转换器的输入数据;信号sncontrol是并串转换器的编码使能时钟。

4 D/A控制模块

D/A控制模块主要用来控制AD9708,对来自串并转换后的数据,FPGA首先进行时分解复用,然后将视频信号部分发送给AD9708,同时配合DAC的转换时钟,该时钟信号是通过并串转换器恢复出来的发射端系统的发射时钟。

结语

此套数字式光端机系统,实现了各个监控点和总监控室的信号远程传输。各监控点的摄像头传回视频信号,总监控室通过485数据接口线对各个摄像头进行远程控制。远程两端之间还可以进行话音通信。具有一定的使用价值和工程意义。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 等电位端子箱是什么_等电位端子箱的作用2025/8/1 11:36:41

- 基于PID控制和重复控制的复合控制策略2025/7/29 16:58:24

- 什么是树莓派?一文快速了解树莓派基础知识2025/6/18 16:30:52

- 什么是有机液分析与有机液知识介绍2025/6/7 16:31:44

- FPGA中的双线性插值算法2025/5/29 17:16:30