多内核导航器+Navigator Runtime应对AMP编程挑战

出处:lianggm 发布于:2012-05-10 09:07:42

引言

多内核处理器给编程人员带来了新的挑战。在多内核项目中,半数以上的成本来自软件开发。多内核编程的具体挑战是非对称多内核处理器 (AMP),因为其中相同的器件中驻留着 RISC与DSP内核等不同类型的处理单元。这主要是因为操作系统 (OS) 对资源管理与负载均衡的支持非常薄弱甚至根本没有,导致可扩展性差与资源利用率低。德州仪器 (TI) 创新型KeyStone II多内核架构提供专用硬件帮助实现调度与负载均衡功能,可简化多内核可编程性。KeyStone II通过这些措施实现了多内核编程的性能突破。

AMP编程挑战

随着多内核技术的演进,越来越多的SoC提供对称多内核架构实现低成本以及更高的性能。典型的AMP具有运行在不同操作系统上的异构内核、硬件加速器以及非所有内核共享的分布式存储器。在对称多内核处理器(SMP)应用中,内核完全相同并运行支持相同共享存储器架构的相同操作系统,因此使用操作系统带来的内核间通信、调度以及负载均衡功能相对而言更为直接。AMP器件的编程需要更高的并行编程技能,才能通过控制和协调不同的内核及操作系统实现可满足单内核或SMP编程需求的高稳定性及高性能。

传统非对称多内核处理要求在编译时对多内核资源进行静态分区。这样做难度往往较大,因为运行时的软件加载不能提前判别,尤其是4G LTE、LTE Advanced以及云计算等技术。一般解决办法是预留额外的空间,以确保系统在恶劣应用条件下也能正确运行。资源过度分配的不利影响是资源利用不足,终会导致产品成本上升。另一方面,首次使用时或者引入新功能、需要现场强化或需求改更时,手动重新分区及软件优化会带来大量的软件工作。

同步性及处理器间通信(IPC)的效率在多内核编程过程中至关重要。缺乏对各种同步性与IPC机制的适当硬件支持,会因过多的软件开销而导致多内核利用低下,降低系统性能。

这对AMP多内核系统而言尤为如此,因为难以实现软件可扩展性与灵活性。

多内核导航器助力实现创新

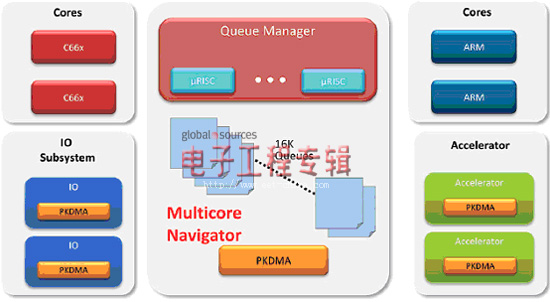

多内核导航器是一种基于数据包的创新基础设施,支持数据传输与多内核控制。TI异构KeyStone架构完美整合了DSP Core-Pac、ARM CorePac、硬件 AccelerationPac以及I/O外设。它们不但可通过TeraNet进行物理互连,而且可通过多内核导航器进行逻辑互连。在TI KeyStone II架构中,多内核导航器不但包含可容纳1.6万个硬件队列的队列管理器,通常存放指向各种数据包(由描述符及数据有效负载组成)的指针,而且还包含8个3,200 MIPS uRISC、用于传输数据的数据包DMA以及支持100万个描述符的硬件数据结构。此外,还可在AccelerationPac与I/O子系统中构建数据包DMA,这样多内核导航器无需内核干预,便可将数据从任何单元传输至任何端点。

多内核导航器为CorePac、AccelerationPac以及I/O提供统一接口,可将硬件队列用于图1所示的不同系统端点。这可为所有IP块提供支持通用通信方式的AMP系统。多内核导航器可充分利用内建在队列管理器中的uRISC内核来管理流量路由、IPC、资源管理、调度以及负载均衡,从而可优化和加速数据流。各种任务可由队列管理器按需派送和分配给负载轻的内核或IP子系统。

图1:多内核导航器子系统

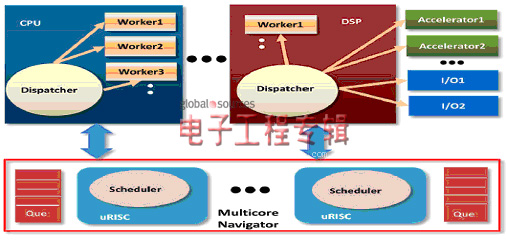

多内核导航器可提供高效率内核间通信机制。硬件队列与数据包DMA是IPC的基本构建块。某些队列经过精心设计,可对IPC内核产生中断。多内核导航器内部的uRISC内核使用可编程中断通知功能实现自动队列监控与管理。多内核导航器可充分限制软件开销,降低同步时延,并可提高IPC吞吐量。此外,它还支持无锁编程模型。图2是使用多内核导航器的IPC示意图。

图2:使用多内核导航器实现处理器间的通信

虽然采用TI KeyStone II硅芯片架构已经解决了多内核挑战,但只有应用软件开发人员充分发挥多内核性能,才能真正实现这种硬件架构的各种优势。在软件方面,TI正在投资标准编程方法,让支持多内核导航器的 KeyStone II 的各项优势充分体现在应用中。行业中及学术界已经涌现出大量有望成为标准的多内核编程趋势。所有这些方法的共同之处在于应用软件开发人员先通过语言表达,采用特定手段描述其应用的并行性,然后再映射至底层运行时。该运行时可掌控将过程映射至底层硬件架构。

Navigator Runtime是一个可扩展薄软件层,可帮助多内核导航器实现更高水平的并行编程性能,提高可扩展性、移植性及效率。对AMP编程挑战而言,多内核导航器和Navigator Runtime的完美结合是一款功能强大的独特解决方案。

Navigator Runtime的主要功能是将工作任务分配给多个内核。先将工作任务放入待执行的虚拟队列,然后由嵌入在多内核导航器硬件中的uRISC内核执行中央调度。调度器根据优先级、原子性以及本地性选择工作任务,然后分配给软件分配器。软件分配器是驻留在每一个内核中的 Navigator Runtime 的必备部件。分配器随即将每项工作任务发送至处理元件执行,处理元件可能是内核、AccelerationPac或I/O端点中的线程。

充分发挥多内核导航器的作用,工作任务制定者及使用者的抽象可由Navigator Runtime完成。将嵌入式uRISC内核用于集中调度工作(无需消耗主DSP或ARM内核的MIPS),可实现低开销、低时延以及每个内核25万个任务的高吞吐量,实现无与伦比的并行编程性能。

图3主要展示Navigator Runtime概念及其与多内核导航器的互动。

图3:Navigator Runtime与多内核导航器的互动

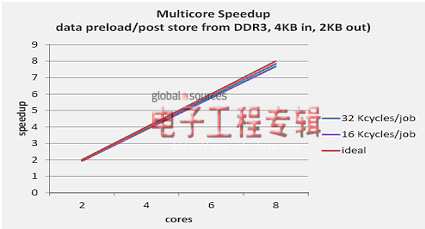

多内核性能可使用加速性进行测量,加速性的定义是用单内核串行执行时间除以多内核执行时间。在理想条件下,8内核系统的加速性等于8.但在实际中,由于多内核总线判优、存储器访问时延、高速缓存一致性管理、同步以及IPC等多内核开销的影响,典型加速性与理想条件相距甚远。Navigator Runtime消耗的开销极少,以尽量接近理想加速性,实现多内核性能的化。

以LTE上行链路物理层处理为例,串行代码可细分为1,024个工作任务用于实现天线数据处理、通道估算以及均衡等。平均每个工作任务有4K输入数据及2K输出数据驻留在共享存储器中。Navigator Runtime将用于调度这些工作任务并分配给8个不同的内核,故加速性的计算如下:

8内核加速性 = 采用本地L2存储器中的数据单内核串行执行代码的时间 ÷ 采用共享DDR3存储器中的数据8内核并行执行的时间

在并行8内核执行示例中,在处理前可分配多个导航器数据包DMA通道将DDR3中的数据预加载到本地L2存储器中,并在处理后将数据从L2返回至DDR3,就像为降低存储器访问时延的 CPU高速缓存运行一样。结果所测得的KeyStone器件的加速性为:在3.2万个周期的工作任务中,从8内核KeyStone器件中测得的基准数据可实现7.8的加速性,而在1.6万个周期的工作任务中,其则可实现7.7的加速性,非常接近理想的8加速性。与KeyStone I相比,KeyStone II中的导航器已得到了明显的改进:4倍uRISC引擎数量可实现更多的调度资源,而数据包DMA通道、硬件队列以及描述符数量翻番,则可提高执行吞吐量。

图4为KeyStone Navigator Runtime在各种工作任务量情况下,2至8内核的实际加速性与理想加速性的比较。

图4:采用Navigator Runtime实现的多内核加速性

此外,TI KeyStone II架构还可为所有异构内核提供6MB的片上共享存储器(MSMC 存储器)容量。MSMC的存储器访问性能非常接近L2存储器访问性能。当数据存储在MSMC中时,无需使用导航器预加载和后存储数据,便可实现与上面情况类似的加速性。与其它可选解决方案相比,大型片上共享存储器可利用低系统时延为多内核性能带来独特的优势。

Navigator Runtime不但可支持各种系统应用,而且还能够与OpenMp等多内核编程范式集成。

OpenMP是一款支持多平台共享存储器多处理编程的应用编程接口(API),由编辑器指令、运行时库程序以及环境变量构成。在OpenMP中,用户可使用语言指令(例如编译器指令)来识别其软件中的并行性,也可使用工具帮助识别。使用兼容OpenMP的编译器可读取编译指令,其可将编译指令所注释的串行代码转换成并行代码,并在OpenMP运行时中插入调用。对在特定器件上运行的应用而言,多内核编程方法的运行时时延及开销性能将会限制可实现的并行性。更低的时延与开销可在应用中实现并行化创造更好的条件,进而实现更高的多内核效率。

开始已经为共享存储器架构指定了OpenMP.我们现在讨论分布式存储器及异构处理器架构支持。TI Navigator Runtime可用作OpenMP的运行时系统。多内核同步与IPC可使用导航器中的数据包DMA引擎有效处理。前面的基准显示,将Navigator Runtime用作OpenMP运行时不但可显着降低编译器指令的构建开销,而且还可显着提升多内核系统内的并行性,让编程人员专注于识别并行任务。调度及负载均衡由Navigator Runtime自动管理,不但可简化编程,而且还可限度地提高多内核效率。

下图5显示的是使用Navigator Runtime与OpenMP的KeyStone AMP编程流程。随同Code Composer Studio集成开发环境提供的Code Gen Tool 7.4版是一款立即可用于OpenMP的编译器。该编程流程具有通用性,不但可用于各种多内核应用,而且还可通过扩展支持各种不同内核及系统规模。其目的是以单内核编程的便捷性实现多内核的高性能。

图5:使用Navigator Runtime的KeyStone AMP编程流程

结论

多内核导航器是一款面向KeyStone器件的创新型智能芯片基础设施,可推动多内核编程的发展。多内核导航器与Navigator Runtime可为每个硬件组件带来抽象性,通过资源管理、调度以及动态负载均衡功能实现平台虚拟化,从而可限度地提高多内核效率,以更低的系统成本实现更高的硬件利用率。将Navigator Runtime与OpenMP等多内核编程模式相结合,可简化AMP多内核软件设计,提高多内核程序的可扩展性与灵活性,并能够以更低的成本快速部署新技术。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 分布式光伏发电有什么优劣势2024/4/29 17:17:39

- 如何更好的理解lwip协议?2024/4/28 17:20:13

- 802.11ac连接的推荐设置_802.11AC无线网桥的配置和注意事项2024/4/28 17:10:43

- matlab是什么编程语言?2024/4/28 17:04:06

- VCC,VDD,VEE,VSS在电源原理图中有什么区别?2024/4/26 17:36:58