基于DSP系统的1553B总线RT设计

出处:电子爱好者博客 发布于:2013-12-25 11:10:50

摘要:1553B总线在航天领域应用越来越广泛,已成为星载有效载荷数据传输的主要途径。为了实现星载有效载荷通过1553B总线传输指令和科学实验数据,选用了以TI公司DSP芯片SMJ320VC33为控制器、DDC公司BU65170为通讯芯片的设计方案。本文所设计的有效载荷具有接口简单、通讯速度快、可靠性高的特点,并已在某星载有效载荷中成功应用,效果良好,对星载1553B总线RT(远置终端)设计具有重要的指导和参考意义。

0 引言

1553B总线是MIL-STD-1553总线的简称,其中B就是BUS.MIL-STD-1553 总线是飞机内部时分制命令/响应式多路复用数据总线,是美国军方专为飞机上设备制定的一种信息传输总线标准,也就是设备间传输的协议。1553B 总线具有一般总线所无法比拟的高可靠性和实时性,在许多重要的科技领域得到了广泛的应用。

近年来,1553B总线在我国许多行业也得到了很好的应用,如航空、航天电子设备,汽车行业和潜艇等。本文以某星载有效载荷为例,选用DDC 公司的BU65170 作为1553B 总线接口芯片,Ti 公司的高速数字信号处理器SMJ320VC33 作为控制器,研制了星载1553B 总线远置终端(Remote Terminal)设备。文中为1553B 总线接口芯片BU65170 和控制器SMJ320VC33 设计了硬件接口连接电路,并对BU65170进行了初始化和软件控制,实现了星上1553B 总线控制器(BC)与有效载荷(远置终端)之间的数据传输。

1 芯片介绍

1.1 BU65170介绍

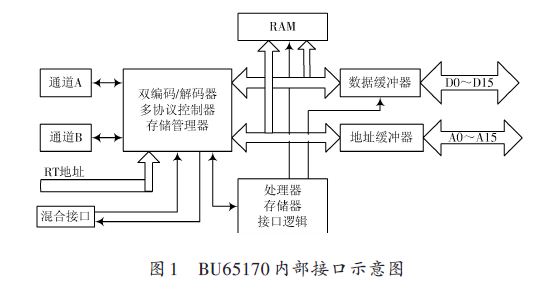

BU65170 是美国DDC 公司推出的第五代1553B 总线产品。它是控制器与1553B 总线之间的智能接口。

BU65170内部结构见图1.

BU65170 可选择在12 MHz 和16 MHz 两种时钟频率下工作。芯片内部具有4K×16 b静态数据存储器及17个功能寄存器。还集成了编码/解码器,双收发器和协议处理器,数据按照一定的协议经编码/解码器处理,通过双收发器A/B来完成与1553B总线间的数据传输,数据传输速率可达1 Mb/s.

协议控制器和存储管理器使BU65170具有许多增强型的功能:数据传输可以选择在单消息、双缓冲、循环缓冲模式下进行。三种数传模式的灵活运用不但能保证指令和数据收发的实时性,还支持大量的数据低误码率的问题;提供对消息的非法检测功能。对于来自总线上的消息,协议控制器根据非法指令表初始化的内容对其进行判断,相应合法的消息,对未启用的消息加以非法屏蔽。这样可大大地提高系统的工作效率。

BU65170 通过中断接口逻辑的控制可产生多种可屏蔽中断。芯片内部集成了中断控制寄存器和中断状态寄存器。中断控制寄存器用来允许活屏蔽不同类型中断,当由中断服务请求时,CPU可以通过查询中断状态寄存器来判断引发中断的消息类型,从而进行相应的控制操作。

BU65170 与MCU 接口简单,可应用8位16位单片机系统,也适用于高速DSP系统,并有多种接口方式,因此得到了广泛的应用。

由于可实现卫星应用的多数单片机数据总线为8 位,而BU65170 数据总线为16 位,因此数据通讯时1个数据字需要执行两次读写操作,通讯效率较低;高速数字信号处理器数据总线一般为16位或32位,并且接口资源更为丰富,与BU65170 连接更为方便,1 次通讯可实现1个数据字的输出,通讯效率高。

1.2 SMJ320VC33介绍

SMJ320VC33是TI公司一款32位高性能的CPU,它是一款应用0.18 μm 四层金属CMOS 技术制造的32 位浮点运算处理器,为用户提供了相当丰富的硬件和软件资源。主要性能指标及内部资源如下:

75 MIPS/150 MFLOPS(时钟75 MHz);片内具有34K×32 b位的静态RAM,既降低了系统的开发成本,又提高了系统的运行速度;独立的程序总线、数据总线和DMA 总线,读写数据和DMA 操作可以并行进行; 采用双电源供电,芯片外围电压3.3 V,核电压仅1.8 V,降低了功耗;具有4个外部中断,中断触发方式有两种:边沿触发和电平触发;具有一个64×32 b的Cache,提高了程序的运行速度;片内存储器可以映射的外设包括1 个串口、2个32 b定时器和一个DMA 控制器;高效的流水线操作。

DSP芯片SMJ320VC33具有速率快、技术成熟、开发周期短等特点,因此在航空、航天等军用电子设备中得到了广泛的应用。SMJ320VC33数据总线宽度为32位,与BU65170连接方式简单、可靠。

2 硬件连接

BU65170 与控制器具有两种连接方式:直接模式(TRANSPARENT MODE)和缓冲模式(BUFFEREDMODE),其中直接模式在BU65170 与控制器之间增加双口RAM,控制器与BU65170之间通过双口RAM 实现数据通讯;缓冲模式下控制器与BU65170直接连接,无需增加双口RAM器件。本方案中BU65170选择缓冲模式与控制器连接,硬件连接框图如图2所示。

主要硬件连接设计如下:BU65170 与SMJ320VC33之间连接方式为缓冲(BUFFER)模式;BU65170安排在SMJ320VC33 地址空间C00000h~FFFFFFh 内,由片选信号PAGE3 选通。BU65170 的片选信号SELECT、STRBD均连接至SMJ320VC33的外设片选信号PAGE3;BU65170 复位信号RESET 通过SMJ320VC33 地址总线扩展得到。DSP上电初始化后对BU65170进行软复位;BU65170的M/R用于存储器、寄存器读写切换(M/R为0时寄存器读写、为1时存储器读写),由SMJ320VC33地址总线A12控制,BU65170读写地址为基址+偏移。寄存器基址为0xC00000,存储器基址为0xC01000;偏移量见BU65170内部存储区分配(如配置寄存器1偏移量为2)。

由于SMJ320VC33 接口电压为3.3 V,而BU65170为5 V,总线接口电压不匹配。因此在数据总线和控制信号(由BU65170 至SMJ320VC33)之间增加电平转换器(5 V←→3.3 V),电平转换器选用UT 公司的UT54ACS164245;SMJ320VC33 读写速度较快,其主频可达75 MHz[4].本文设计工作主频为60 MHz,对应读写短周期分别为16.6 ns和33.2 ns(读操作占用1 个机器周期,写操作占用2个机器周期),而BU65170读写周期约为200 ns,因此二者之间读写时序不匹配。

SMJ320VC33具备两种读写工作模式:软等待模式和硬等待模式,具体由总线控制寄存器配置控制。其中软等待模式下多可将读写操作延长至8个机器周期,对应读写时间约为132 ns(60 MHz主频);硬等待模式读写时间由外设决定,此模式下SMJ320VC33通过查询RDY脚电平状态判断读写操作是否完成(RDY 脚为低电平时读写操作完成,高电平时等待)。本文设计为硬等待模式,将BU65170 的READYD 经过电平转换之后连接至SMJ320VC33的RDY 脚;BU65170的INT脚连接至控制器SMJ320VC33 的外部中断3.当接收到消息时,BU65170的INT脚会产生一个中断信号(电平或边沿触发),表明有通讯消息发生。SMJ320VC33 对BU65170相应存储器进行读操作,判别接收到的消息类型,并作出相对应的响应;BU65170通过耦合变压器与1553B总线连接,耦合变压器选用DDC 公司的B3226,信号耦合系数比为1∶2.5;BU65170 时钟选择16 MHz 工作模式,16 MHz时钟由有源晶振ZA519提供。

3 软件设计

本系统软件采用模块化的设计思路,主要由初始化、主循环模块构成。

3.1 初始化模块

程序初始化包括2 部分内容:DSP 初始化和BU65170初始化。

3.1.1 DSP初始化

DSP 初始化主要对SMJ320VC33内部寄存器(中断寄存器IE、IF、ST,定时器、总线控制寄存器等)、IO扩展口及内部RAM等进行初始化。

3.1.2 BU65170初始化

BU65170启动工作之前需要对其进行初始化,主要对BU65170工作模式、消息处理模式和其他相关寄存器进行配置,同时对各子地址查找表进行配置。初始化顺序为:子地址查找表配置→存储区配置→寄存器配置。

子地址查找表分为A、B两个区,分别独立设置(互为备份、冗余)。每个区又分为接收查找表、发送查找表及广播查找表。

查找表定义初始化流程如图3所示。图3中Roffse-tA,ToffsetA,RT_SAA分别为A区接收、发送及广播查找表;RoffsetB,ToffsetB,RT_SAB分别为B区接收、发送及广播查找表。子地址共32个。

BU65170内部含4K×16 b数据存储器,包含消息接收堆栈、查找表及数据存储区。其中消息接收堆栈用于存储消息命令字,查找表用于消息数据字存储地址链接(1 553 B消息数据字存储地址),数据存储区用于存储1 553 B消息数据字。初始化时首先对A、B区查找表按照BU65170用户手册进行定义及地址配置,之后设置各子地址消息数据字存储地址(将数据字存储地址写至相应查找表);通过子地址控制字启用设计需要的子地址,对对未启用的子地址进行屏蔽。数据存储区配置完成之后对其进行初始化(一般为清零)。

寄存器初始化需要按照一定的顺序进行(如顺序不对,则BU65170不正常工作)。BU65170内部共包含17个寄存器,初始化只涉及其中7个寄存器。本设计寄存器初始化顺序及设置见表1.

寄存器由上至下顺序进行初始化。初始化时对上述寄存器进行单字写操作。

3.2 主循环模块

主循环模块用于完成对1553B 消息的响应及处理。对于一般的RT 而言,消息一般分为3 类:指令消息、数据传输消息及校时消息。其中指令消息(BC 向RT发送)可包含多条,也可只设置一条(一个子地址可同时包含多条指令数据,指令数据字组成指令数据包);数据传输消息(RT向BC发送数据)可包含多条,也可只设置一条(一个子地址也可包含种数据,数据字组成数据包)。

当RT 接收到来自BC 的已定义、合法的消息时,BU65170 会向SMJ320VC33 产生中断,通知SMJ320VC33 已接收到消息,请求处理。控制器SMJ320VC33首先对消息接收堆栈进行读操作,读取消息命令字,同时对消息命令字进行解析,以获取消息子地址及数据字长度信息,对消息类型进行判断,根据消息类型执行相应的响应。指令消息、校时消息需要读取数据字信息,数据发送消息需要将待发送的数据(有效载荷的科学实验数据)写入至相应的存储地址(BU65170内部)。主循环模块流程如图4所示。

4 结语

本文基于DSP 系统的1553B 总线RT 设计,选用的DSP为Ti公司的高速信号处理器SMJ320VC33.该设计充分发挥了SMJ320VC33内部资源丰富、接口简单的优点。同时,SMJ320VC33 具有计算速度快的优点,满足了有效载荷的高速数据采集、处理需求。该设计已在某星载有效载荷中成功应用,应用结果表明:该系统具有开发简单、性能稳定的特点,可应用于各类星载1553B总线RT的设计。(作者:崔阳,李增科)

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 接口测试的测试点有哪些类型2025/8/12 16:58:37

- MicroUSB接口转接头使用指南2025/8/11 17:03:03

- 一文详解IIC总线2025/8/7 17:10:39

- 保护接地和保护接零有什么区别2025/8/7 16:54:43

- lc和sc接口哪个更耐用2025/8/5 17:19:22