汽车音响导航系统中DDR高速信号的PCB设计

出处:维库电子市场网 发布于:2014-09-01 19:22:56

在以往汽车音响的系统设计当中, 一块PCB上的时钟频率在30~50MHz已经算是很高了,而现在多数PCB的时钟频率超过100MHz,有的甚至达到了GHz数量级。为此,传统的以网表驱动的串行式设计方法已经不能满足今天的设计要求,现在必须采用更新的设计理念和设计方法,即将以网表驱动的串行的设计过程, 改变成将整个设计各环节并行考虑的一个并行过程。也就是说将以往只在PCB布局、布线阶段才考虑的设计要求和约束条件, 改在原理图设计阶段就给予足够的关注和评估,在设计初期就开始分析关键器件的选择,构想关键网线的拓扑结构,端接匹配网络的设定, 以及在布线开始前就充分考虑PCB的叠层结构,减免信号间的串扰方法,保证电源完整性和时序等因素。

本文主要介绍在汽车音响导航系统中使用的高速DDR200,在兼顾高速电路的基本理论和化设计经验的指导下, 保证信号完整性的PCB设计方法。

1. 什么是DDR 及其基本工作原理

DDR SDRAM,习惯称为DDR.DDR SDRAM即双倍速率同步动态随机存储器。

DDR内存是在SDRAM 内存基础上发展而来的。SDRAM在一个时钟周期内只传输数据, 它是在时钟的上升期进行数据传输;而DDR内存则是一个时钟周期内传输两次数据, 它能够在时钟的上升期和下降期各传输数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到双倍的数据传输率。

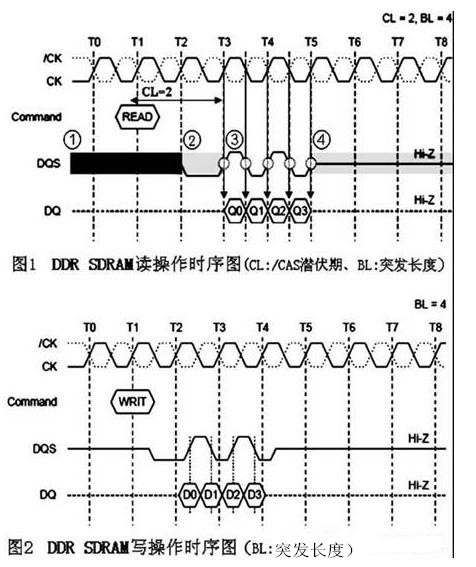

如下图1和图2所示,DDR SDRAM相对SDRAM多了两个信号: CLK# 与DQS。

CLK# 与正常CLK时钟相位相反, 形成差分时钟信号。而数据的传输在CLK与CLK# 的交叉点进行, 即在CLK的上升与下降沿(此时正好是CLK#的上升沿)都有数据被触发,从而实现双倍速率传输。

DQS(DQ STrobe、数据选取脉冲)是DDRSDRAM中的重要功能, 主要用来在一个时钟周期内准确的区分出每个传输周期,并在接收端使用DQS来读出相应的数据DQ。

DQS在上升沿和下降沿都有效,与数据信号同时生成。DQS和DQ都是三态信号双向传输。在读操作时,DQS信号的边沿在时序上与DQ 的信号边沿处对齐, 而写操作时,DQS信号的边沿在时序上与DQ信号的中心处对齐。

下面以图1-DDR SDRAM读操作时序图为例,说明DQS的控制原理:

①在没有数据输出的状态时,DQS处于高阻抗水平。

② 接到READ指令后,DQS信号变为低阻抗, 并较数据输出时间提前一个周期。

③ D Q S 信号在CLK与CLK# 的交叉点与数据信号同时生成,频率与CLK相同。

④DQS信号持续到读脉冲突发完了为止,完了后再度恢复到高阻抗水平。

2. 基本规格

DDR SDRAM的基本规格(表1)。

表1 DDR SDRAM的基本规格

3. DDR200 的PCB 设计方法

下面以汽车音响导航系统中使用的DDR200为例,从PCB叠层结构的选择、布线拓扑结构、串扰、电源完整性和时序等方面考虑的PCB设计方法。

3.1 PCB叠层结构的选择

线路板的叠层结构直接决定了信号在各导体层的传输速度及延迟时间。根据电路构成及结构限制,结合高速信号及电源的返回路径等EMI要求,在设计初期确定好叠层结构以及重要信号的布线层是十分重要的。本例的叠层结构及重要信号的布线层如图3 所示。

根据板材不同, 导体铜厚, 各绝缘层厚及介电常数等也会有差异,导致高速信号传输线的特性阻抗Zo及传输延时Tpd的不同。

板材中绝缘介质的介电常数εr=4.0,绝缘层厚PP1=60μm,PP2=200μm,PP3=800μm,导体铜厚35μm,且线宽W=100μm时,信号在表层(L1、L6)的传输延时Tpd≒140ps,特性阻抗Zo≒56Ω,在内层L3布线的传输延时Tpd≒170ps,特性阻抗Zo≒84Ω。

3.2 DDR SDRAM信号的布线标准

为控制传输线的阻抗及延时等的影响, 要先确定以下的布线设计标准:

*高速信号线条宽度,以保证传输线特性阻抗值:差分信号Zo 100Ω,其他信号Zo≒50Ω。

*为减少传输线间的串扰,确定间距值。实际布线时要尽可能加大间距。

*可用过孔的孔直径及过孔焊盘直径:

①Build-up积层激光冲压孔②内层盲埋孔(L2到L5使用)③通孔(L1到L6用)④各种过孔焊盘间间距。

3.3 DDR SDRAM器件的布局结构图

DDR的数据传送通常是一个发射端对应多个接收端的结构, 为实现数据的同步传送,延迟时间的控制尤为重要。在构建器件Layout的时候重点考虑传输线分歧节点的选定,各段传输长度相等等要求。如图4,将DDR 相关电路中的元器件都放在同一个面上, 并通过“ 星型及Y 型拓扑结构”实现CLK、Data数据组,及Address/Command等各数据组之间的等长布线控制。

3.4 高频信号的布线优先顺序

依照设计要求的严格程度从重要的信号线开始布起,顺序为:

CLK→Data→Address/Command

3.5 CLK差分信号的布线方法

针对DDR200中使用的CLK差分信号,布线拓扑图如图5 .布线注意点如下:

①差分阻抗要实现100Ω。

② 差分对CLK与CLK# 要等长布线,但总长度不要过长。

即CLK( A - B - C 1 - D 1 ) = CLK( A - B -C1-D2)= CLK( A - B - C 2 - D 3 ) = CLK( A - B -C2-D4)3.6 DATA组的布线方法。

图5 CLK布线拓扑图

如图6, 标明了DATA组所选的布线拓扑图。布线注意点如下:

① 所有D A T A 信号从N A V I - C P U出发到每个D R A M 的长度都要相等( 即A - B - C段)。

②等长布线的误差可以按同一Bit列及各组Bit间的误差来控制,如表2。

图6 DATA数据组的布线拓扑图

表2

3.7 Address/Command的布线方法

如图7,标明了Address/Command组所选的布线拓扑图。布线注意点如下:

① 总布线长( A - B - C - D ) 等长, 且与CLK间的长度误差控制在一定范围内。

②D段(D1,D2,D3,D4)的布线要等长。

图7 Address/Command数据组的布线拓扑图

3.8 等长布线的设计方法

为实现DATA组、Address/Command组等网线的等长控制,可以采用曲线(或称矩形线)的布线方法。但若曲线的长度过长或曲线间宽度DM过短,会因为电磁场间的耦合导致信号的传输延迟短于预想时间,过早被传送到接收端,造成信号传输不等时的现象。

3.9 电源与地的布线方法

DDR200所使用的电源有2.5V、3.3V、Vref、Vtt等。布线注意点如下:

①Vref作为输入Buffer用的基准电压,要避免混入其他信号的噪音。布线时要同时注意同层信号间的耦合及相邻上下层间的耦合问题。还要避免跟Vtt(终端电压)的互相干扰。尤其在本例的叠层结构中,要注意与第3层CLK线的层间耦合影响。

②为降低Vtt的走线阻抗,尽可能增加布线宽度,推荐铺电源面。

4. 结语

本文在DDR200工作原理的基础上介绍了实现设备高性能的PCB设计方法。如今数字电路已经出现了更高速的DDR2 及DDR3,希望本文的设计思路及高速信号的布线方法能对大家的设计有所帮助。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- MPS推出车规级三相栅极驱动器IC新产品2025/8/12 11:15:06

- CAN XL 通信技术在车载毫米波雷达的卓越应用2025/8/8 16:20:47

- 泰克 EA 电源串联技术:推动 800V 电动汽车高压架构快速发展2025/8/6 11:02:56

- RIGOL 方案:为车载电驱功率半导体动态性能测试保驾护航2025/7/31 16:36:01

- 英飞凌 TLD7002 - 16ES:减少车灯控制器 MCU 数量,实现成本优化新方案2025/7/25 16:21:14