加法器电路原理图解

出处:维库电子市场网 发布于:2016-12-27 15:32:01

二进制加法器是数字电路的基本部件之一。二进制加法运算同逻辑加法运算的含义是不同的。前者是数的运算,而后者表示逻辑关系。二进制加法是“逢二进一”,即1+1=10,而逻辑加则为1+1=1。

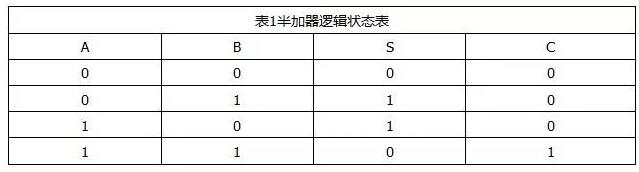

1、半加器

所谓“半加”,就是只求本位的和,暂不管低位送来的进位数。半加器的逻辑状态表见表1。

表1半加器逻辑状态表

其中,A和B是相加的两个数,S是半加和数,C是进位数。

由逻辑状态表可写出逻辑式:

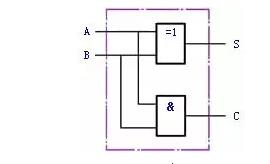

并由此画出图1(a)的逻辑图。图1(b)是半加器的逻辑符号。

(a)逻辑图

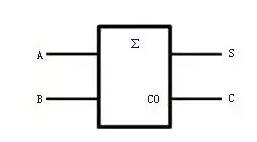

(b)逻辑符号

图1半加器逻辑图及其逻辑符号

2、全加器

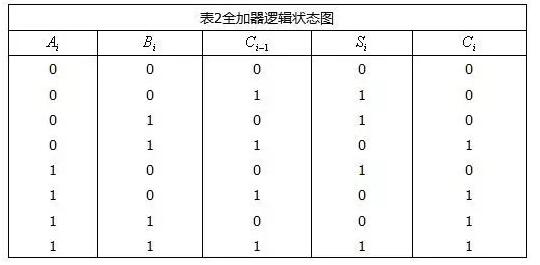

当多位数相加时,半加器可用于位求和,并给出进位数。第二位的相加有两个待加数,还有一个来自低位送来的进位数。这三个数相加,得出本位和数(全加和数)和进位数,这就是“全加”,表2是全加器的逻辑状态表

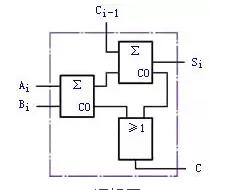

全加器可用两个半加器和一个或门组成,如图2(a)所示。在个半加器中相加,得出的结果再和在第二个半加器中相加,即得出全加和。两个半加器的进位数通过或门输出作为本位的进位数。图2(b)是全加器的逻辑符号。

(a)逻辑图

(b)逻辑符号

图2 全加器逻辑图及其逻辑符号

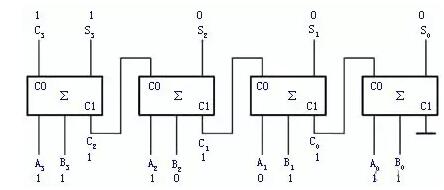

例1、用4个全加器组成一个逻辑电路以实现两个4位的二进制数A—1101(十进制为13)和B—1011(十进制为11)的加法运算。

解:

逻辑电路如图3所示,和数是S—11000(十进制数为24)。根据全加器的逻辑状态表自行分析。

这种全加器的任意一位的加法运算,都必须等到低位加法完成送来进位时才能进行。这种进位方式称为串行进位,它的缺点是运算速度慢,但其电路比较简单,因此在对运算速度要求不高的设备中,仍不失为一种可取的全加器。T692集成加法器就是这种串行加法器。

图3 例1的逻辑图

上一篇:反激式变压器开关电源电路参数计算

下一篇:关于DC/DC电源和EMI的讨论

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 提高低功率 AC/DC 转换的效率并减小尺寸2024/4/29 17:02:26

- 串联电路与并联电路的区分2024/4/25 17:15:00

- 查找隔离栅极驱动器的峰值电流2024/4/25 17:07:48

- 使用 GaN IC 离线电源的大容量电容器优化2024/4/24 17:30:57

- 并联电压电池2024/4/23 17:45:00