DMA缓存解耦的一点见解

出处:维库电子市场网 发布于:2016-09-13 16:28:06

DMA(英文全称:Direct Memory Access,中文:直接内存访问)是一种不经过CPU而直接从内存存取数据的数据交换模式。在DMA模式下,CPU只须向DMA控制器下达指令,让DMA控制器来处理数据的传送,数据传送完毕再把信息反馈给CPU,这样就很大程度上减轻了CPU资源占有率,可以大大节省系统资源。

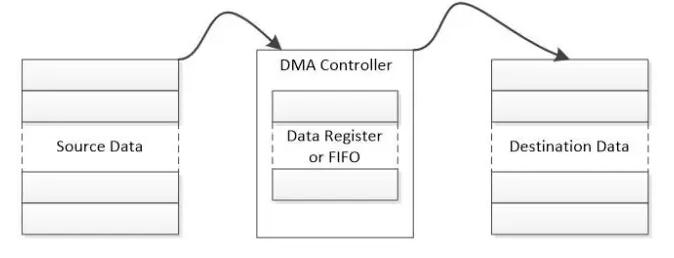

DMA的传输模型结构见下图:

Figure 1 DMA传输模型

从上图可知,使用DMA从源地址传输数据到目的地址,数据都必须通过DMA控制器内部的寄存器或FIFO作缓存,而不是在源和目的地之间直接传输,这是因为源和目的所在设备的传输速度不一样,接口也不一样,要适应这些情况,数据在DMA控制器内的缓存是必不可少的,这样可使在低速设备传输数据时,高速设备可被释放并可被重新利用,这可看作是一种解耦,使低速设备和高速都能高效工作而不相互影响。

笔者在工作过程中,曾遇到一个有关DMA的issue,具体如下:在某个应用使用DMA进行大数据量传输过程中,经常出现数据传输异常,检查系统的调试打印信息,发现DMA在阶段性传输结束(会产生相应的中断)后,重新启动新阶段的DMA传输(使用相同的通道)时,有时会出现申请的DMA通道还在活动状态的情况,导致后面的数据传输无法正常启动。按照一般的思路,驱动程序设置好参数,启动DMA后,就可以去做其他工作,中断的到来就意味着该次的DMA传输结束了,但矛盾的是有时发现传输结束的DMA通道却不在空闲状态,要说明的是,所有的DMA通道资源都是预先分配好的,不同驱动程序使用各自不同的通道,不会互相干扰。开始认为是驱动程序没有设计好,出现竞争导致函数重入,但阅读整个驱动源码后,没有发现这方面的问题。

重新分析整个DMA传输过程:数据从源设备到目标设备,中间是要经过DMA controller Data transfer register或FIFO这个中转站暂存,而中断产生的条件是只要源或目的地址更新到与通知地址相同,这样当中断发生时,的数据可能还在中转站内,传输还在进行当中,由于的数据传输什么时候能真正结束,取决于目标器件以及当时的总线仲裁等情况,时间比较随机,此时中断服务函数重新启动新阶段传输前检查该通道时就有可能查询到DMA通道还处于忙状态,这样就会导致重新启动DMA通道失败而无法继续进行数据传输。

初步认为issue的产生是由于真正的数据传输结束滞后于DMA中断的产生(这个应该是硬件设计的一个bug),因此解决的方法就是加入等待,这可以通过多次重复查询来实现。按照这个思路,修改驱动程序,重新进行测试,问题没有复现,数据传输正常,这说明以上的分析推断是正确的。

通过上面的例子可以看到,充分理解DMA设计的一些硬件基本机理,对我们在工作当中解决一些实际问题还是很有帮助的。

上一篇:信号逻辑电平标准详解

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 锁相环的基本概念2024/4/23 17:56:14

- 信号与系统分析简介2024/4/16 17:03:33

- 使用逻辑信号、交流耦合和接地栅极驱动 CMOS 图腾柱2024/4/10 16:54:32

- 什么是射频?什么是射频信号?2024/4/7 17:53:28

- 探索光耦合器替代方案2024/3/29 17:04:49

- 英特尔数据存储如何操作和实现

- 什么是微动开关_微动开关有什么用_微动开关使用方法

- VCC,VDD,VEE,VSS在电源原理图中有什么区别?

- 低压配电系统设计规范_低压配电系统设计注意事项

- xEV 主逆变器电源模块中第四代 SiC MOSFET 的短路测试

- 光耦详细应用教程

- 定义绝缘耐久性评估的电压脉冲测试要求

- 采用沟槽MOS结构,使存在权衡关系的VF和IR相比以往产品得到显著改善 ROHM推出实现业界超快trr的100V耐压SBD“YQ系列”

- NOVOSENSE - 纳芯微推出车规级温湿度传感器NSHT30-Q1,助力汽车智能化发展

- Keysight - EV 电池设计创新:扩大续航里程、延长电池寿命