基于FPGA的串行A/D转换模块设计

出处:维库电子市场网 发布于:2017-12-19 14:33:46

电子技术发展的数字化进程中,A/D转换器性能起到了关键的作用,使用硬件描述语言来设计数字电路方便快捷,FPGA的时钟频率可高达300MHz以上,A/D转换控制逻辑简单,故可用FPGA器件进行控制设计。除了一些专用引脚外,FPGA芯片上几乎所有引脚均可供用户使用,这使得FPGA信号处理方案具有非常高性能I/O带宽,大量的I/O引脚和存储器让系统拥有出色的并行处理能力,完成A/D转换等功能。

1、系统设计

本设计采用FPGA芯片XC3S250ETQG144来对TLC549进行采样控制,并对采样数据进行处理。

1.1、Spartan-3E型FPGA

XC3S250ETQG144处理器是FPGA的Xilinx公司下Spartan-3E系列的一款中高端配置的低成本处理器,其具体参数如下图所示:

图1芯片参数

其单位逻辑单元的成本达到更低的水平,适用于对逻辑单元需求多,对I/O需求少的设计,端口电压为3.3V、2.5V、1.2V,驱动电流16mA,支持DDR存储接口,具有片上匹配终端的增强型差分信号[3],其与TLC549的连接管脚为10、11、15.

1.2、TLC549芯片介绍

美国德州仪器公司生产的TLC549,是低价位、高性能8位串行A/D转换芯片,它以8位开关电容逐次逼近A/D转换器为基础而构造的CMOSA/D转换器,能通过3态数据输出和模拟输入与微处理器或其他外围设备串行接口,仅用输入/输出时钟(I/OCLOCK)和芯片选择(CS)输入作为数据控制,是低成本的测控应用系统。具备4MHz片内系统时钟和软硬件控制电路,长转换时间是17us,TLC549可以达到快45000次/S的速率,总失调误差为±0.5LSB,典型功耗值为6mW.差分参考电压高阻输入的方式,抗干扰,可按比例量程校准转换范围,VREF-接地,VREF+—VREF-≥1V,TLC549适用于较小信号的采样工作。

小编推荐:

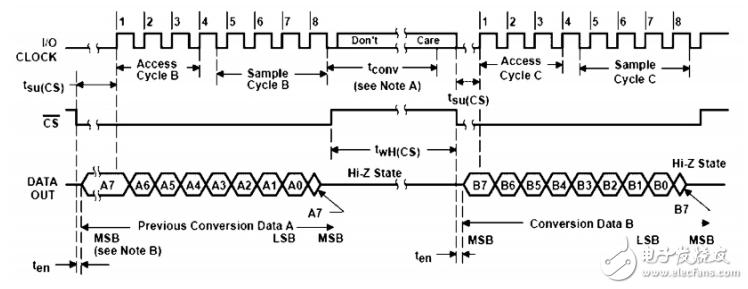

TLC549均有片内系统时钟,该时钟与I/OCLOCK是独立工作的,无需特殊的速度或相位匹配,下图是它的工作时序图:

图2TLC549工作时序图

转换过程需要36个系统时钟周期,为17us,它开始于CS变为低电平之后I/OCLOCK的第8个下降沿。在CS变为低电平之后,有效位(A7)自动被放置在DATAOUT总线上。其余的7位(A6-A0)在前7个I/OCLOCK下降沿由时钟同步输出。B7-B0以同样的方式跟在其后。

1.3、设计原理

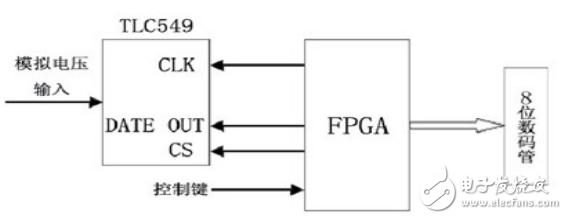

TLC549的控制信号相对较少,用FPGA芯片XC3S250ETQG144对TLC549进行采样控制及A/D转换,控制器设计原理图如图3所示。

图3 控制器设计原理框图

通过3态数据输出和模拟输入与外围设备串行接口,通过CLK和片选CS进行数据控制,模拟电压值通过信号预处理端和滤波设计等进入到TLC549,通过FPGA的控制等功能,实现硬件功能上电压值的8位数码管显示。TLC549的硬件连接如图4所示。

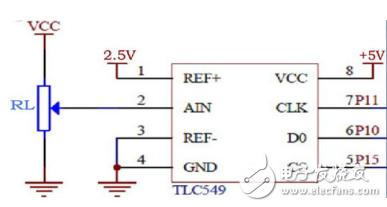

图4 TLC549与FPGA硬件连接图

1脚为基准电压输入,可以采用LM317进行稳压设计,为A/D转换提供的时钟基准源,1脚接2.5V,2脚接电位器,根据模拟电压的输入值,调整模拟电压输入,以此改变数据输出显示,3,4脚接地。通过图3可以看到,芯片的CLK、CS、DATEOUT三条口线与FPGA主控芯片进行串行接口,实现A/D转换的整个过程,其中8脚接+5V直流为芯片供电。

2、模块设计与仿真

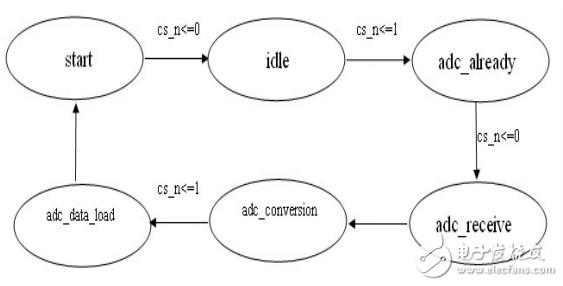

利用VerilogHDL语言设计的TLC549转换电路控制器的关键在于如何将TLC549的工作时序抽象成状态转移图,从而由状态机来实现。

状态机是由寄存器和组合逻辑构成的硬件时序电路,其状态只能在同一时钟跳变的情况下才能从一个状态转向另一个状态。它的步骤一般包括:逻辑抽象,得出状态装换图;状态化简;状态分配;选定触发器的类型并求出状态方程、驱动方程和输出方程,按照方程得出逻辑图。参照TLC549的工作时序图,可得到图5的TLC549的转换电路控制器的状态转移图,状态机的每次跳变不但取决于各个输入值,还跟当前状态有关。

图5 TLC549转换电路控制器的状态转移图

如图所示,start状态表示开始数据转换,之后系统初始化,其中idle为空闲状态、adc_ready为A/D转换准备状态、adc_receive为A/D数据的接收状态、adc_conversion为A/D转换进行状态,adc_data_load为数据输出状态。系统初始化后,由片选端控制,进入空闲状态,使能端置1,进入数据转换准备状态,CS信号拉低进入到数据接收状态,随着数据读取完毕,A/D转换继续进行直至数据输出转换结束,这就是整个A/D转换的流程。由此,可以着手于TLC549模块的A/D转换代码编写阶段了。

设计输入测试的为A/D转换程序模块,clock为系统时钟,复位reset为高电平有效,enable为转换使能,TLC549为串行数据输入,clk为I/O时钟,CS为片选控制端,data_out为转换的数据输出,数据信号同步输入,数据输出锁存。图6为顶层模块图。

图6 TLC549顶层模块图

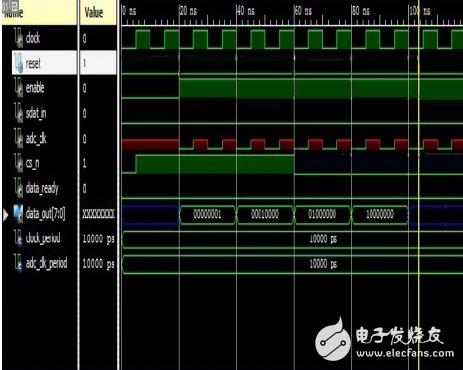

在完成verilogHDL代码的输入,程序调试后,经过分析、综合,排除错误,以达到设计要求。随后再进行波形仿真,在工程管理区将sourcesfor设置为simulaTIon后,双击IsimSimulaTIon下的SimulateBehavioralModel,系统会自动调用Isim仿真功能,仿真波形图如图7所示,通过与图2的TLC549芯片的工作时序图的相比较,发现该仿真图达到了实际要求的效果。

图7 仿真波形图

从图7的仿真波形可以看出,上端为时钟周期,初始化后,片选端cs_n转换状态data_ready为0表示转换并未开始,5ns片选端后置1,使能端也为1,进入转换准备状态,和系统时钟保持一致,转换开始,随后A/D转换数据接收状态,转换继续进行直至转换数据输出。

3、结语

用VerilogHDL语言和Xilinx公司的FPGA芯片XC3S250ETQG144,设计了TLC549的采样实例,该FPGA芯片通过并行接口的方式与计算机连接,体现了FPGA的高速度和VerilogHDL语言并行执行程序的特点,克服了传统单片机A/D转换速度慢的弊端,为具体的硬件设计提供了参考。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 有没有适配m1的模拟器2025/8/11 16:55:19

- ADI 即插即用型 D 类放大器的卓越特性与优势2025/8/8 16:36:07

- 深入解析共集、共基、共射放大器的奥秘2025/8/2 10:49:20

- 线性霍尔 IC 全解析:原理、应用与优势2025/7/25 16:16:43

- 模拟音频耳机和数字音频耳机的区别2025/7/17 17:19:59