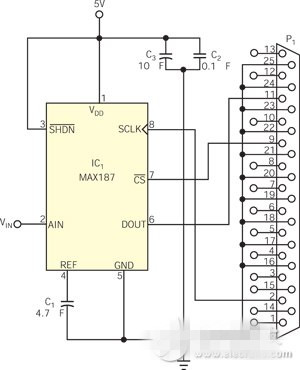

基于12位串行ADC与PC之间的接口电路设计

出处:电子发烧友 发布于:2019-05-06 14:20:13

完整的数据传输需要13个外部时钟脉冲。个时钟脉冲的下降沿锁存DOUT引脚(引脚6)的个数据位(MSB)。输出数据位在下一个外部时钟脉冲的下降沿就改变,可以读取串行数据位,直到下一个时钟周期的下降沿出现为止。模/数转换在ADC的引脚(引脚7)变成低电平时开始进行。该引脚必

须保持低电平,直到模/数转换整个周期结束为止,随后进行串行数据传输。DOUT引脚从低电平至高电平的状态变化表示EOC(转换结束)状态。然后,串行的12位数据就可以进行传输了。MAX187的工作情况由软件控制。该软件应能产生成功完成转换所需的所有控制信号,而且应能检测EOC状态。它还应能产生13个外部时钟脉冲,以便读取串行12位数据并将其转换成并行数据。

控制MAX187工作情况的软件是Turbo C++ 3.0版本(可从网站的《设计实例》的Web版本)。在代码中,Port定义与MAX187接口的PC的 Centronics端口。Write Port定义用于初始化模/数转换和产生外部时钟脉冲的端口。Read Port定义用于从ADC读取EOC和串行数据的端口。在将CS引脚和SCLK引脚下拉至低电平后,EOC环路检查EOC状态。如果未出现有效的EOC,则该环路将继续工作。有效EOC出现,13个时钟周期中的个周期就出现,并锁存个数据位(MSB)。此后,例行程序调用一个子例程(get_adc())。子例程产生剩下的外部时钟周期,以便读取12位串行数据。子例程还将接收到的串行数据转换成并行数据(adc_val)。这一转换过程为:使adc_val左移一位,由此将前一个数据乘以2,如果串行数据位的值为1,则将1加到并行数据上。一旦并行数据就绪,子例程将返回这个值并将其显示在屏幕上。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 一文详解IIC总线2025/8/7 17:10:39

- 保护接地和保护接零有什么区别2025/8/7 16:54:43

- lc和sc接口哪个更耐用2025/8/5 17:19:22

- RS232与RS485接口的详细区别对比2025/7/31 17:01:52

- lan接口和wan接口有什么区别2025/7/31 16:44:47