CMOS传输门的边沿触发器电路结构及工作原理

出处:电子发烧友 发布于:2019-07-12 14:50:12

CMOS D触发器足主-从结构形式的一种边沿触发器,CMOS T型触发器、JK触发器、计数单元、移位单元和各种时序电路都由其组成,因此仪以CMOS D触发器为例进行说明。

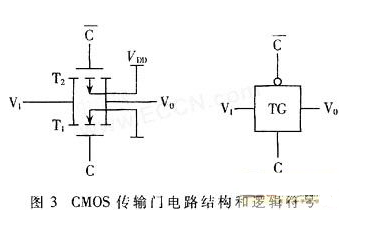

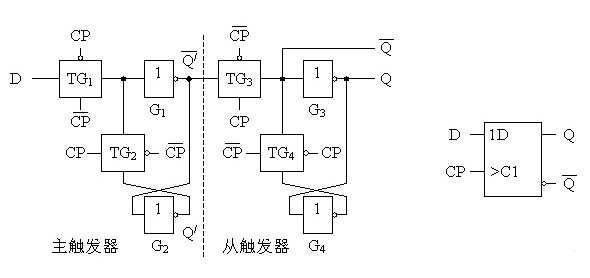

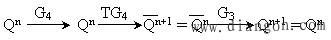

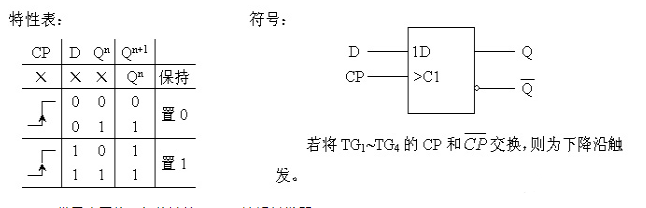

图1是用CMOS传输门和反相器构成的D触发器,反相器G1、G2和传输门TG1、TG2组成了主触发器,反相器G3、G4和传输门TG3、TG4组成了从触发器。TG1和TG3分别为主触发器和从触发器的输入控制门。反相器G5、G6对时钟输入信号CP进行反相及缓冲,其输出CP和CP′作为传输门的控制信号。根据CMOS传输门的工作原理和图中控制信号的极性标注可知,当传输门TG1、TG4导通时,TG2、TG3截止;反之,当TG1、TG4截止时,TG2、TG3导通。

当CP′=0,CP′=1时,TG1导通,TG2截止,D端输入信号送人主触发器中,使Q′=D,Q′=D,但这时主触发器尚未形成反馈连接,不能自行保持。Q′、Q′跟随D端的状态变化;同时,由于TG3截止,TG4导通,所以从触发器形成反馈连接,维持原状态不变,而且它与主触发器的联系被TG3切断。

当CP′的上升沿到达(即CP′跳变为1,CP′下降为0)时,TG1截止,TG2导通,切断了D信号的输入,由于G1的输入电容存储效应,G1输入端电压不会立即消失,于是Q′、Q′在TG1截止前的状态被保存下来;同时由于TG3导通、TG4截止,主触发器的状态通过TG3和G3送到了输出端,使Q=Q′=D(CP上升沿到达时D的状态),而Q=Q′=D。

在CP′=1,CP′=0期间,Q=Q′=D,Q=Q′=D的状态一直不会改变,直到CP′下降沿到达时(即CP′跳变为0,CP′跳变为1),TG2、TG3又截止,TG1、TG4又导通,主触发器又开始接收D端新数据,从触发器维持已转换后的状态。

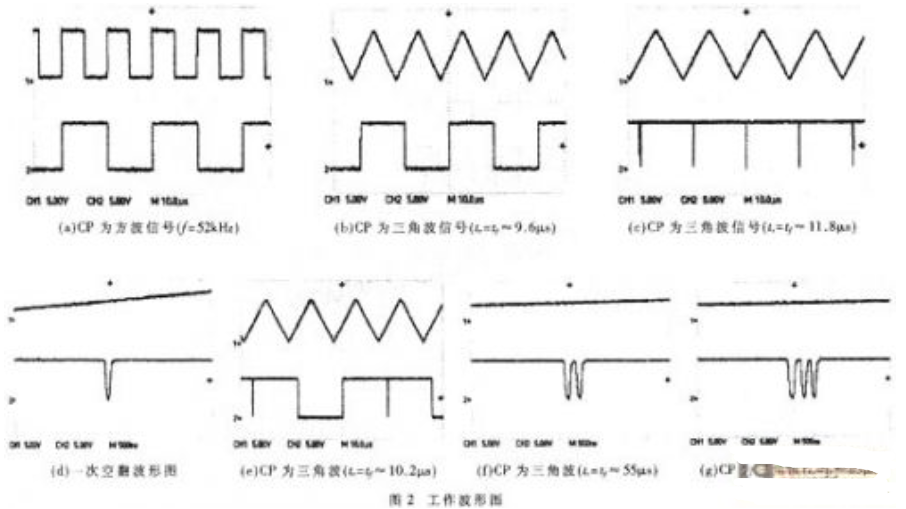

可见,这种触发器的动作特点是输出端的状态转换发生在CP′的上升沿,而且触发器所保持的状态仅仅取决于CP′上升沿到达时的输入状态。正因为触发器输出端状态的转换发生在CP′的上升沿(即CP的上升沿),所以这是一个CP上升沿触发的边沿触发器,CP上升沿为有效触发沿,或称CP上升沿为有效沿(下降沿为无效沿)。若将四个传输门的控制信号CP′和CP′极性都换成相反的状态,则CP下降沿为有效沿,而上升沿为无效沿。下面以CP上升沿为有效触发沿进行分析。

1、电路结构

2、工作原理

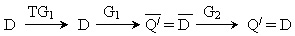

(1)CP=0, =1时:TG1导通,TG2截止,TG3截止,TG4导通

Q/随D变化:

TG3截止,则:

从触发器保持

(2)CP:0→1,TG1截止,TG2导通,TG3导通,TG4截止

由于G1的电荷存储效应,G1输入端的电压不会立刻消失,Q/在TG1切断前的状态得到保存。

即CP上升沿到达时D的状态

3、动作特点:

输出端状态的转换发生在CP上升沿,触发器所保存下来的状态仅取决于CP上升沿到达时的输入状态。

输入信号为单端D,所以也叫D触发器

CMOS传输门的边沿触发器电路结构及工作原理

P199 ,带异步置位、复位端的 CMOS 边沿触发器。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 什么是MOS管?NMOS、PMOS和三极管的区别2024/4/30 17:17:10

- MOSFET 开关损耗简介2024/4/29 16:52:06

- 信号二极管详细教程2024/4/28 16:20:03

- ROHM 6432尺寸金属板分流电阻器“PMR100”新增3款超低阻值产品!2024/4/28 15:26:33

- 光耦详细应用教程2024/4/26 16:43:32