基于CPLD器件MAXII EPM1270和PCI总线实现数据接收卡的设计

出处:微计算机信息 发布于:2020-12-08 15:23:07

PCI9656支持66Mhz、64bit的PCIR2.2规范,提供了兼容PICMG2.1R2.0规范的CompactPCIHotSwap接口,其局部总线达到66MHz、32bit(支持0“66MHz、8/16bit),可为PCI(CompactPCI)适配器及嵌入式系统设计提供高性能的总线接口。PCI9656的配置寄存器与PCI9054、PCI9056兼容,也方便了原有设计的移植。

PCI9656具有6条独立的数据通道,用于DirectMaster、DirectSlave以及DMA功能模式下的数据传输,其深FIFO设计有效提升了总线的突发传输性能。

1DirectMaster模式。用于局部总线到PCI(CompactPCI)的数据传输,16QWords(128byte)和32QWords(256byte)的FIFO各应用于数据的读、写通道。

2DirectSlave模式。用于PCI(CompactPCI)到局部总线的数据传输,16QWords(128byte)和32QWords(256byte)的FIFO各应用于数据的读、写通道。

3DMA模式。PCI9656提供了两条DMA通道(Channel0、Channel1),使用了两独立的32QWords(256byte)双向FIFO。两条DMA通道可同时传输数据,通过PCI9656的MARBR寄存器可配置其优先级关系。PCI9656的DMA方式有常规的块模式(Blockmode)和集散模式(Scatter/Gathermode),而且支持以DREQ#、DASK#信号请求、应答的命令模式(Demandmode),可应用于通信领域中的实时数据传输。

在局部总线端,PCI9656简化了数据的传输控制逻辑,与ISA总线类似,方便了传输控制的设计实现。PCI9656的局部总线有三种应用模式,可以适用不同的嵌入式处理器。

1M模式。支持Motorola32bit的处理器,提供了可与MPC850、MPC860PowerQCICC直接相连的接口。

2C模式。适合大多数处理器的通用模式,在设计中多采用此模式。

3J模式。与C模式类似,但其地址线与数据线复用。

2数据接收卡设计

PCI9656片内资源丰富,功能多样,采用PCI9656为接口芯片,可方便地进行PCI(Compact)适配器的设计。而在PCI9656的局部总线端,往往不需要实现其全部逻辑功能,可依据需要选取配置,更进一步简化设计。

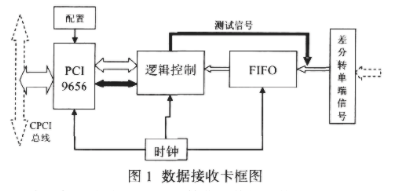

图1是应用PCI9656的CompactPCI数据记录卡的设计框图,此数据接收卡应用于一款合成孔径雷达的数据记录器中,数据源为34bit的差分信号,32bit数据,1bit采样时钟,1bit数据有效标志位。图1中:时钟驱动ICS553向PCI9656、逻辑控制模块和FIFO提供同步时钟信号;初始化配置芯片采用Microchip93LC56B,PCI9000系列提供3线的E2PROM串行接口,可在系统上电时初始化内部配置寄存器;差分到单端信号的转换经由TI公司的LVDT386和390完成;FIFO采用了IDT公司所设计的高速、低功耗的72T36135M,数据容量为512K×36bit,使用易于级联的FirstWordFollowThrough工作模式;逻辑控制部分采用Altera的MAXIIEPM1270,实现FIFO到PCI9656局部总线间的数据传输控制。

2.1PCI9656的设计应用

在CompactPCI端,PCI9656提供了66MHz、64bit总线应用所需信号,可依据CompactPCI规范连接,通过简单的外部电路,可实现HotSwap功能。

在局部总线端,采用了PCI9656的C模式。在C模式下,PCI9656的局部总线可配置实现三种数据传输逻辑。(1)Singlecyclemode。每次传输1个数据(8/16/32bit),默认的传输模式。(2)Burst-4mode。每次4个数据,应用Inteli960与IBMPPC401处理器时的推荐模式。(3)ConTInuousburstmode。多数据的连续突发传输模式,提供了 的数据吞吐量。在传输过程中,从设备(Slave)可通过Bterm#信号停止传输过程。模式2与模式3只选其一,模式1始终可用。在数据接收卡中,采用了连续突发(ConTInuousburst)模式,可以有效的利用局部总线带宽。

分析接收卡的设计:局部总线端无处理器,PCI9656在此端为主设备(Master),始终占用总线,负责逻辑控制的CPLD为从设备(Slave),始终响应PCI9656。数据传输过程只利用了PCI9656的DirectSlave和DMA模式,,而且不需DMA的命令模式,运行过程中数据通过FIFO单向传输,不需解码地址信号,对CPLD的控制可通过向其写命令码完成。因此,可以对PCI9656的许多信号简化处理,只需实现如下信号的时序要求:

pIYBAF_O6oOAHgxaAAC1eiExBUw158.png

LD[31:0],32bits数据信号。

ADS#,总线操作的开始标志。

Blast#,突发传输的结束标志。

LW/R#,写/读信号。

Wait#,主设备暂停传输信号,信号无效标志主设备正常。

Ready#,从设备操作完成信号,信号有效标志从设备正常。

EOT#,数据传输异常中止信号,用于FIFO溢出或空时中断数据传输。

Lint#,中断信号输入,用于引起CompactPCI总线端的中断。

LRST#,局部总线端重置。

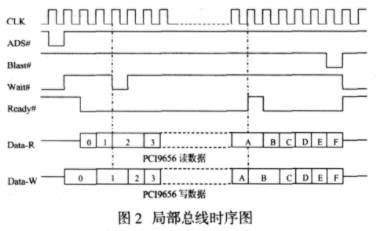

信号经简化后,在正常的读写操作中,只需要处理ADS#、Blast#、LW/R#、Wait#、Ready#与数据的逻辑关系,Singlecycle可认为是ConTInuousburst的特例,从而将两种模式下的逻辑时序统一处理。正常操作中,ADS#、Blast#、Wait#、Ready#需满足的逻辑关系如图2所示:

图2中,ADS#、Blast#、Wait#信号由PCI9656驱动,LW/R#(图2中未标出)也由PCI9656驱动,在整个过程中处于低或高,标志PCI9656对总线的读或写操作。Ready#由CPLD驱动,Data为双向信号。CPLD空闲状态时监测ADS#信号,一旦ADS#有效,则根据LW/R#转入读或写操作。读操作中,CPLD将FIFO数据读出,同时将Ready#置为有效状态,需监测Wait#,Wait#无效时,才可继续读取下一数据;写操作中,CPLD需将Ready#置为有效状态,监测Wait#,Wait#无效时,CPLD才可完成总线上数据的写入;当CPLD检测到Blast#、Wait#、Ready#均为有效状态时,便完成 一个数据的传输操作,转至空闲状态。

实现上述的数据传输逻辑,再加上适当的异常情况和测试转换控制,便可设计CPLD的逻辑控制模块。

2.2MAXIIEPM1270应用

MAXII系列是Altera公司的新型架构CPLD,与传统架构的CPLD相比,MAXII的功耗和成本大幅降低,资源密度和性能却显著提升,非常适用于接口间的控制协议转换。设计中采用了MAXII的EPM1270型号CPLD,其设计结构如图3所示。MAXIIEPM1270内部主要分为逻辑控制、测试、FIFO三个模块:

o4YBAF_O6omAB4POAACO_ehQkuk311.png

1FIFO采用Altera提供的IP核实现,容量可根据资源利用情况调节,使用FWFT(FirstWordFollowThrough)模式,为CPLD提供与外部FIFO简便的接口。

2测试模块产生测试数据,控制数据通道在真实数据源与测试数据源间切换,在测试接收卡时使用。

3逻辑控制模块内有异常和测试控制、状态转换控制两部分,通过一个8bit寄存器进行通信。(1)寄存器控制CPLD的测试模块、状态选择,同时记录FIFO的状态变化。(2)异常和测试控制部分依据状态寄存器内容控制测试模块,监测FIFO的溢出、半满、空等状态,产生Lint#信号或通过控制寄存器传递到状态转换控制部分,使之有效EOT#,中断数据传输。(3)状态转换控制部分执行局部总线的数据读写逻辑,建立了四个状态:S0,空闲状态;S1,数据读状态;S2,寄存器读状态;S3,命令写状态。S0状态下根据LW/R#信号和寄存器内容确定向S1、S2、S3状态的转换。S1状态下读取FIFO数据,根据FIFO状态产生异常中止信号EOT#。S2状态下读取8bit寄存器内容。S3状态下向8bit寄存器写入命令码来改写和重置其相关比特位,从而控制CPLD的测试模块,切换S1、S2状态,清空FIFO。

通过上述设计模块,MAXIICPLD便可在PCI9656与IDT72T36135M之间建立一个简捷的数据传输通道。

3结束语

PCI9656采用了PLX公司业界 的数据通道架构技术,其丰富的功能为高速的PCI(CompactPCI)总线应用提供了简捷的I/O设计途径。文章介绍了采用PCI9656作为PCII/O设计的一款应用于66Mhz、64bitCompactPCI总线系统的数据接收卡。本文作者创新点:1将PCI9656应用于66Mhz、64bitCompactPCI总线系统,满足高速数据传输的要求。2采用CPLD内建FIFO的IP核实现FIFO与PCI9656的接口连接,优化了CPLD的转换逻辑。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 一文详解IIC总线2025/8/7 17:10:39

- 保护接地和保护接零有什么区别2025/8/7 16:54:43

- lc和sc接口哪个更耐用2025/8/5 17:19:22

- RS232与RS485接口的详细区别对比2025/7/31 17:01:52

- lan接口和wan接口有什么区别2025/7/31 16:44:47