大电流线性电源(LDO)原理的超详细解读

出处:厂商供稿 发布于:2021-07-19 14:26:33

NMOS LDO工作简介

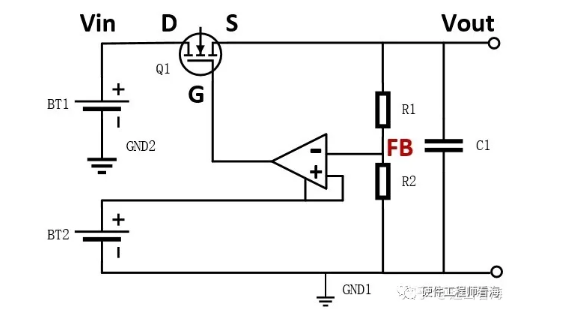

下图是一个NMOS LDO的基本框图,NMOS LDO一般也工作在饱和区(特殊时会在可变电阻区),所以Vg要大于Vs,因此NMOS LDO除了有Vin引脚,一般还会有个Vbias引脚来给MOS G极提供高压驱动源;或者只有一个Vin,而内部集成了CHARGE BUMP来为G极提供高压驱动源。大体工作流程同PMOS LDO:当Vout下降时,反馈回路中的Vfb也会下降,误差放大器输出端Vg就会增加,随着Vg增加,Ids电流也增加, 终使得Vout又恢复到原始电平,状态如下:

Vout↓-->Vfb↓-->Vg↑--Iout↑-->Vout↑

2. NMOS LDO详细工作原理

下图是某NMOS输出特性曲线,让我们结合上图和下图分析,当Vout下降,Vin不变,则Vds=Vin-Vout,Vds增加,MOS工作点由A转移到B;紧接着反馈回路开始工作,Vfb电压减小,经过误差放大器后,Vg增加,那么Vgs=Vg-Vs,Vgs也增加,从下图可以看到,随着Vgs增加,MOS的电流Id逐渐上升,进而使得Vout逐渐升高,MOS工作点由B转移到C,LDO又回到原始工作电平。

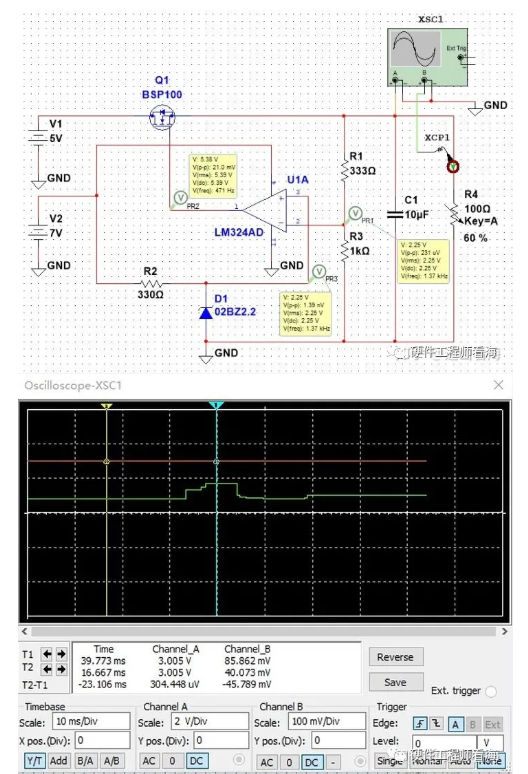

3. NMOS LDO仿真结果

下图是简单的5V转3.0V的NMOS LDO仿真图以及仿真波形结果,橙色曲线是电压,绿色曲线是电流,随着负载端滑动变阻器R4的变化,负载电流也在变,而输出电压基本稳定在3.0V。

4. LDO 输出电容你知道多少?

考虑到系统的稳定性,LDO的输出电容原则上是要加的,但是如果对于成本有 的考虑,在满足一定要求时,这个电容其实是可以删除的。

5. Dropout voltage

上文分析了PMOS LDO工作在恒流区(饱和区),DS之间有一定的压差,此压差常称为dropout voltage(Vdo),所以LDO若想稳定工作在饱和区,输入输出之间满足一定的压差,应用中通常可以考虑在spec中预留25%的余量。比如下图中在Iout=150mA时,不同Vout对应的Vdo也不同。

大电流线性电源(LDO)原理的超详细解读

6. 效率

效率此处不过多讨论,LDO自身消耗的功率约等于压差*电流,因此相同负载电流下,压差越大,LDO功耗越高,所以压差稍微低一些,有利于提高效率。

7. PSRR

LDO重要参数之一也是巨大优点之一便是纹波小,即PSRR好,PSRR是电源抑制比,是LDO对输入电源纹波的抑制程度,PSRR的 值越大越好。看PSRR曲线有个转折点,左边为LDO自身起主导作用,右边为输出电容起主导作用,PSRR性能好的LDO左边的曲线会更高,加大输出电容,右边的曲线会升高。

LDO的基本原理与介绍可以告一段落了,而其内部实际工作情况是非常复杂的,本文只起引导作用,希望能引起大家的共鸣或排解一些疑惑,欢迎关注我的公众号:硬件工程师看海。里面会定期更新鲜的内容。

上一篇:开关模式电源电路图合集

下一篇:电源系统的过电压类别

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 电源设计故障防护:现代保护 IC 的简单解决方案2025/8/5 16:10:25

- 电源噪声的来源与应对策略2025/8/4 16:31:13

- 直流可编程电源串联或并联连接的优势2025/8/4 16:25:37

- 解析 BUCK 电路:负载电流增大时电感纹波电流的变化2025/7/31 15:59:18

- 深度解析 DC-DC 电源 PCB 设计关键要点2025/7/30 16:50:03