上拉和下拉电阻的6个要点

出处:mouser 发布于:2022-02-21 14:46:24

Q:在电路中,上拉和下拉电阻有什么作用?

A:电阻在电路中起限制电流的作用。上拉电阻和下拉电阻是经常提到也是经常用到的电阻。在每个系统的设计中都用到了大量的上拉电阻和下拉电阻。概括来说上拉和下拉电阻的作用主要有以下6点:

上拉电阻和下拉电阻的主要作用

1. 提高电压准位

当TTL电路驱动CMOS电路时,如果TTL电路输出的高电平低于CMOS电路的很低高电平,这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值;OC门电路必须加上拉电阻,以提高输出的高电平值。

2. 加大输出引脚的驱动能力

有的单片机引脚上也常使用上拉电阻。

3. N/A引脚(没有连接的引脚)防静电、防干扰

在CMOS芯片上,为了防止静电造成损坏,不用的引脚不能悬空,一般接上拉电阻降低输入阻抗,提供泄荷通路。同时引脚悬空就比较容易接收外界的电磁干扰。

4. 电阻匹配

抑制反射波干扰,长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻使电阻匹配,能有效的抑制反射波干扰。

5. 预设空间状态/默认电位

在一些CMOS输入端接上拉或下拉电阻是为了预设默认电位。当不用这些引脚时,这些输入端下拉接低电平或上拉接高电平。I2C等总线上空闲时的状态是由上下拉电阻获得的。

6. 提高芯片输入信号的噪声容限

输入端如果是高阻状态,或高阻抗输入端处于悬空状态,此时需要加上拉或下拉电阻,以免受到随机电平的影响,进而影响电路工作。同样,如果输出端处于被动状态,需要加上拉或下拉电阻,如输出端仅仅是一个三极管的集电极,还可以提高芯片输入信号的噪声容限,增强抗干扰能力。

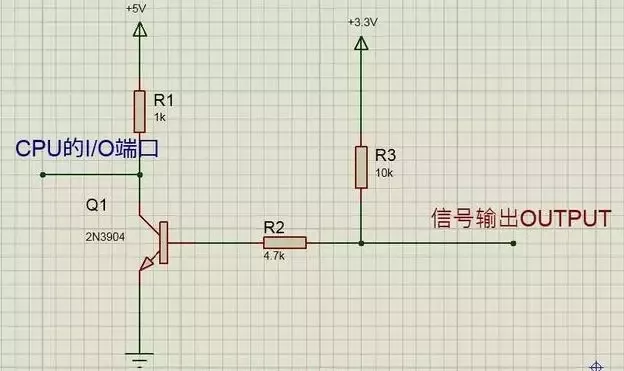

在BJT晶体三极管的基极端,上拉电阻和下拉电阻也起着至关重要的作用。在三极管的电路应用中,串接在基极上的电阻起限制基极电流的作用,如图1中的R2所示:

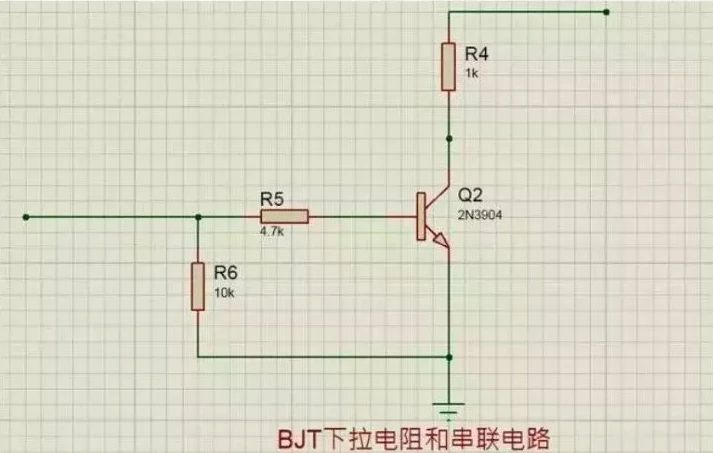

如图2中的R5所示,上拉电阻使三极管基极的输入电平在默认情况下是高电平输入,当CPU有低电平信号输出时,外围电路响应,下拉电阻使晶体管的基极输入在默认情况下拉到低电平,如图2中的R6所示。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- MOSFET 开关损耗简介2024/4/29 16:52:06

- 信号二极管详细教程2024/4/28 16:20:03

- ROHM 6432尺寸金属板分流电阻器“PMR100”新增3款超低阻值产品!2024/4/28 15:26:33

- 光耦详细应用教程2024/4/26 16:43:32

- 采用沟槽MOS结构,使存在权衡关系的VF和IR相比以往产品得到显著改善 ROHM推出实现业界超快trr的100V耐压SBD“YQ系列”2024/4/26 15:56:19