数字音频信号如何传输:I2S协议

出处:玩转嵌入式 发布于:2022-12-23 13:45:19

支持全双工/半双工

支持主/从模式

和PCM相比,I2S更适合立体声系统。I2S的变体也支持多通道的时分复用,因此可以支持多声道。

主机Master、从机slave

对于系统而言,产生SCK和WS的信号端就是主设备,用MASTER表示。

I2S有3个主要信号

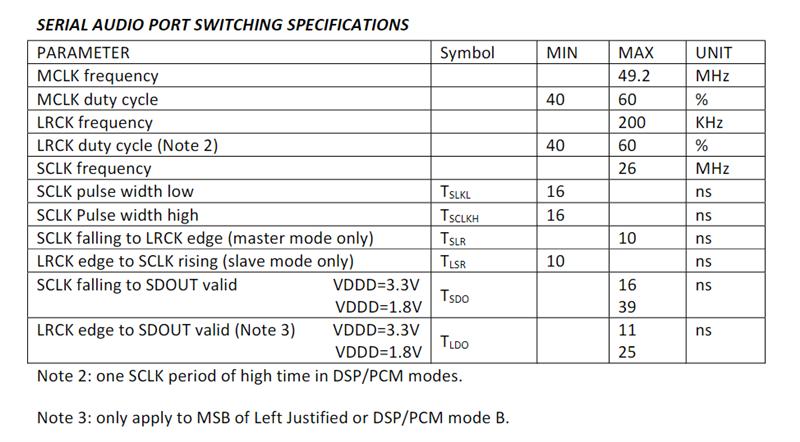

SCLK(BCLK):串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数。

LRCK:帧时钟LRCK,(也称WS),用于切换左右声道的数据。LRCK为“1”表示正在传输的是右声道的数据,为“0”则表示正在传输的是左声道的数据。LRCK的频率等于采样频率。

串行数据SDATA:就是用二进制补码表示的音频数据。位拥有固定的位置,而位的位置则是依赖于数据的有效位数。

MCLK:称为主时钟,也叫系统时钟(Sys Clock),一般为了使系统间能够更好地同步时增加MCLK信号,是采样频率的256倍或384倍。

数据在上升沿有效时(被读取),信号只会在CLK为下降沿变化,上升沿时保持稳定状态。

随着技术的发展,在统一的 I2S接口下,出现了多种不同的数据格式。

根据SDATA数据相对于LRCK和SCLK的位置不同,分为左对齐-MSB、I2S格式(即飞利浦规定的格式)和右对齐-LSB(也叫日本格式、普通格式)。

对于所有数据格式和通信标准而言,始终会先发送有效位(MSB 优先)。发送端和接收端必须使用相同的数据格式,确保发送和接收的数据一致。

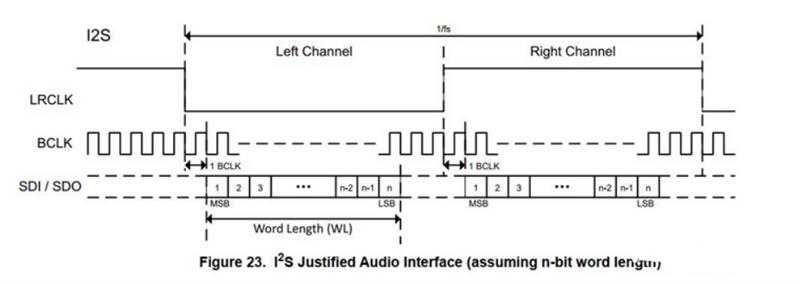

I2S格式

对于这种标准I2S格式的信号,无论有多少位有效数据,数据的位总是出现在LRCLK变化(也就是一帧开始)后的第2个BCLK脉冲处。这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

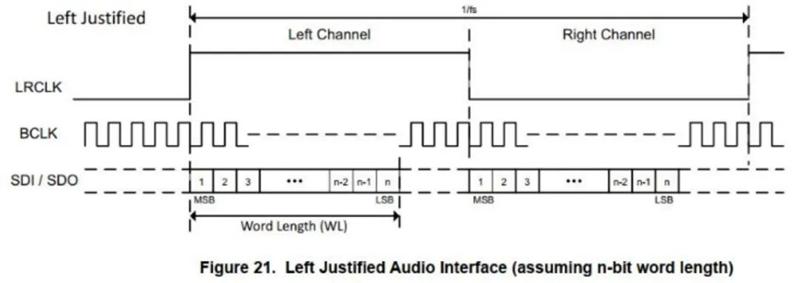

左对齐-MSB

在LRCLK发生翻转的同时开始传输数据。该标准较少使用。注意此时LRCLK为1时,传输的是左声道数据,这刚好与I2S Philips标准相反。左对齐(MSB)标准时序图如下所示:

声音数据LSB传输完成的同时,LRCLK完成第二次翻转(刚好是LSB和LRCLK是右对齐的,所以称为右对齐标准)。注意此时LRCLK为1时,传输的是左声道数据,这刚好与I2S Philips标准相反。右对齐(LSB)标准时序图如下所示:

上一篇:高频噪声从信号中滤除的有效方法

下一篇:运放电路的比例运算

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 基于罗氏线圈电流传感器:ADC 信号链灵敏度的全面解析2025/8/7 16:19:31

- 什么是光耦隔离?光耦隔离有何作用?2025/8/4 16:57:05

- 揭秘共模滤波器:精准区分信号与噪声的原理2025/7/29 16:22:37

- 攻克多天线系统测试难题:三种相位相干射频信号生成策略揭秘”2025/7/28 16:38:12

- FSK调制工作原理2025/7/25 17:00:17