如何使用去耦电容放置来减少谐波失真

出处:维库电子市场网 发布于:2023-04-12 17:40:08

不良的电容器去耦会增加失真

PCB 的电源和接地导体确实存在一些电感。如果我们试图直接通过电源和接地导体提供设备的高频电流,这种电感可能会导致问题。

回想一下,电感两端出现的电压降与电流变化率成正比。因此,在更高的频率下,电源和接地导体上会出现相对较大的电压降,我们将无法为 IC 提供恒定的电源电压。

对于高速运算放大器,电源电压的变化将取决于信号,因此线性性能将显着降低。

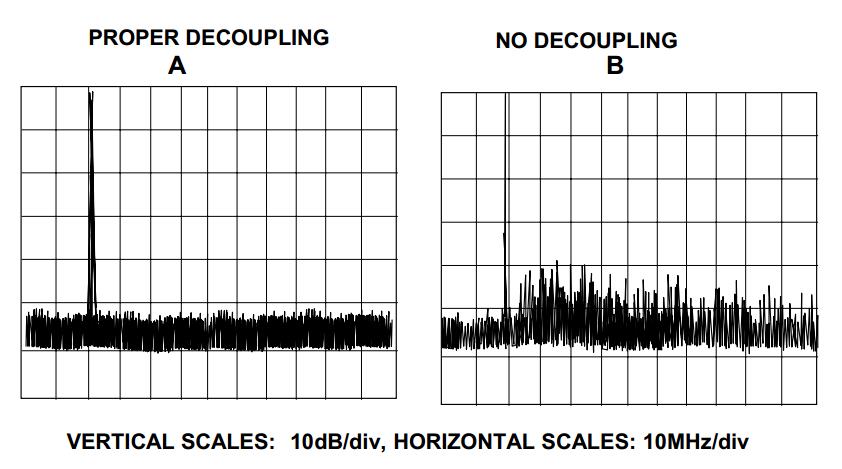

为了解决这个问题,我们将去耦电容器放置在靠近运算放大器电源引脚的位置。作为电荷源,去耦电容器提供高频电流并显着减少电源电压的变化。下图显示了驱动 100Ω 负载的 AD9631 运算放大器输出端的频率内容。

图 1.具有适当去耦(左)和无去耦(右)的 AD9631 运算放大器的频谱输出。图片由Analog Devices提供。

如您所见,通过适当的去耦,失真分量会大大减少。

使电容接地端子远离运算放大器输入

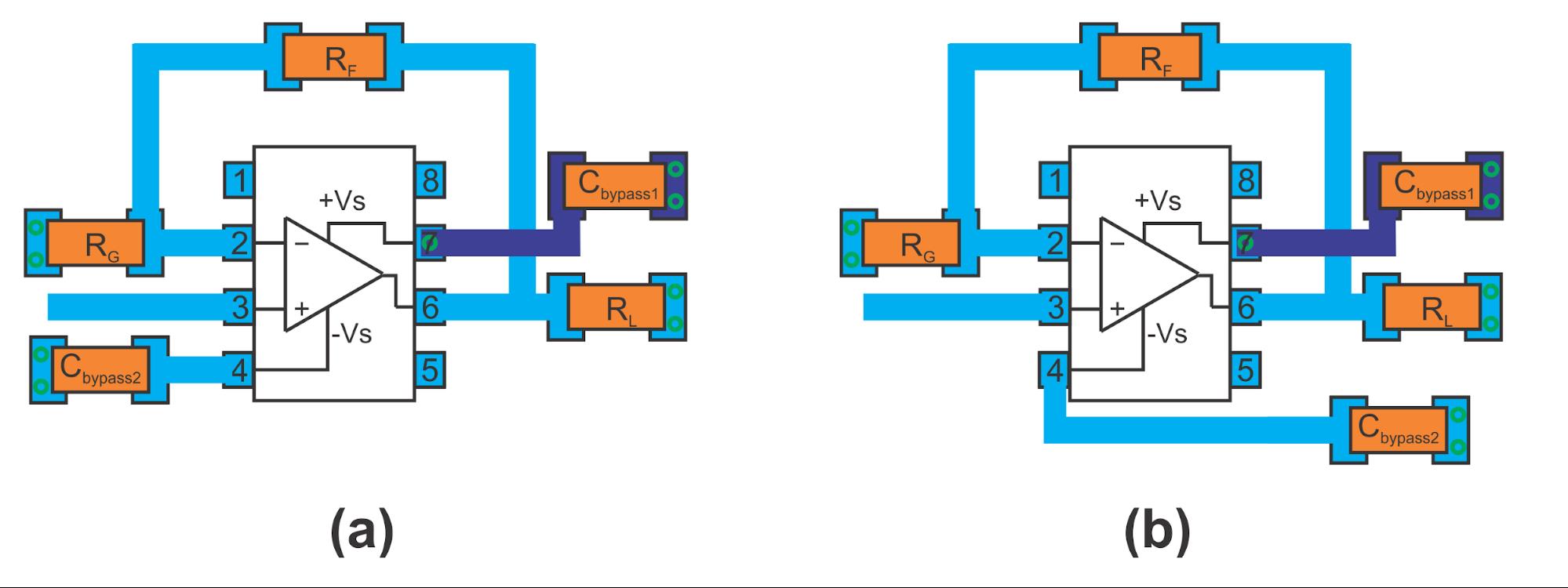

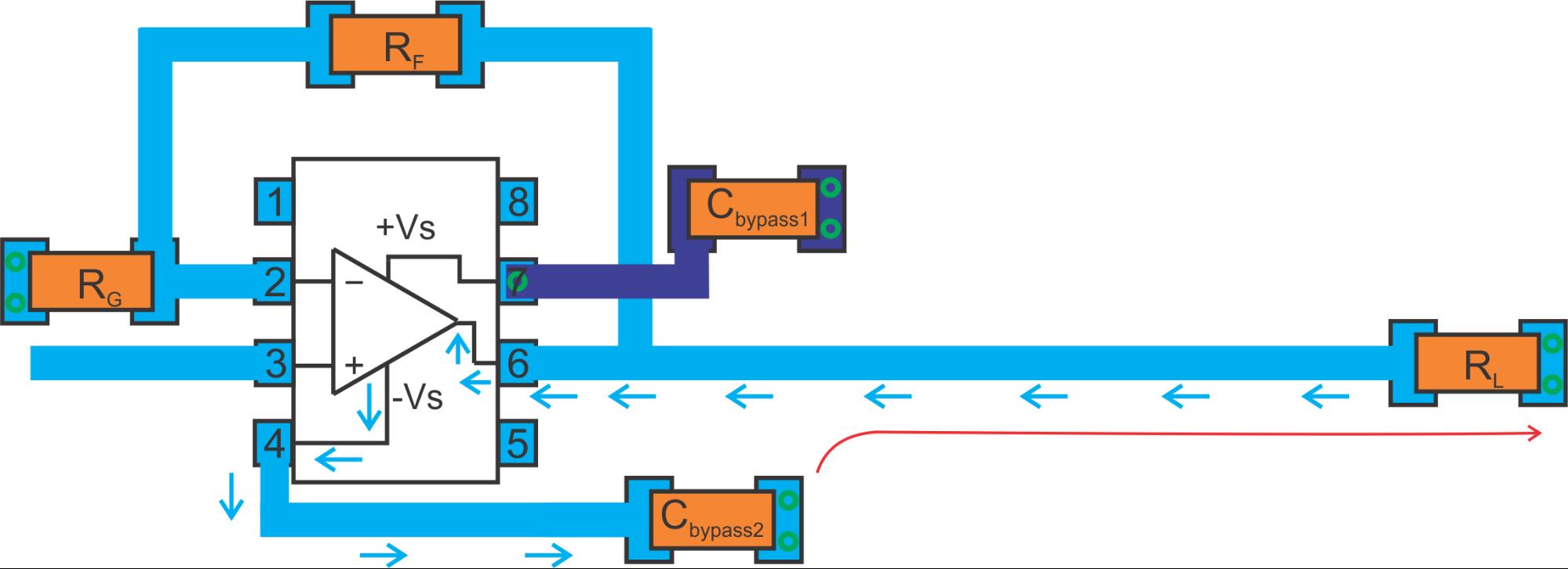

PCB布局是优化高速板失真性能的关键因素。考虑下面所示的布局示例,了解在 SOIC 封装中使用运算放大器的非反相放大级。

在这些示例中,所有组件都放置在电路板的顶部,只有正轨 (C bypass1 ) 的旁路电容器位于底部。我们假设电路板有专用接地层,绿色圆圈表示的过孔将迹线或焊盘连接到该接地层。

图 2. 负轨旁路电容器位置不同的两个电路图。

如您所见,除了负轨旁路电容器 (C bypass2 )的放置外,这两种布局完全相同。左侧的布局将 C旁路 2的接地侧靠近运算放大器输入,而右侧的布局试图使该端子靠近负载并远离运算放大器输入。

图 2(b) 中的布局可以实现更好的失真性能。

仔细注意返回电流路径

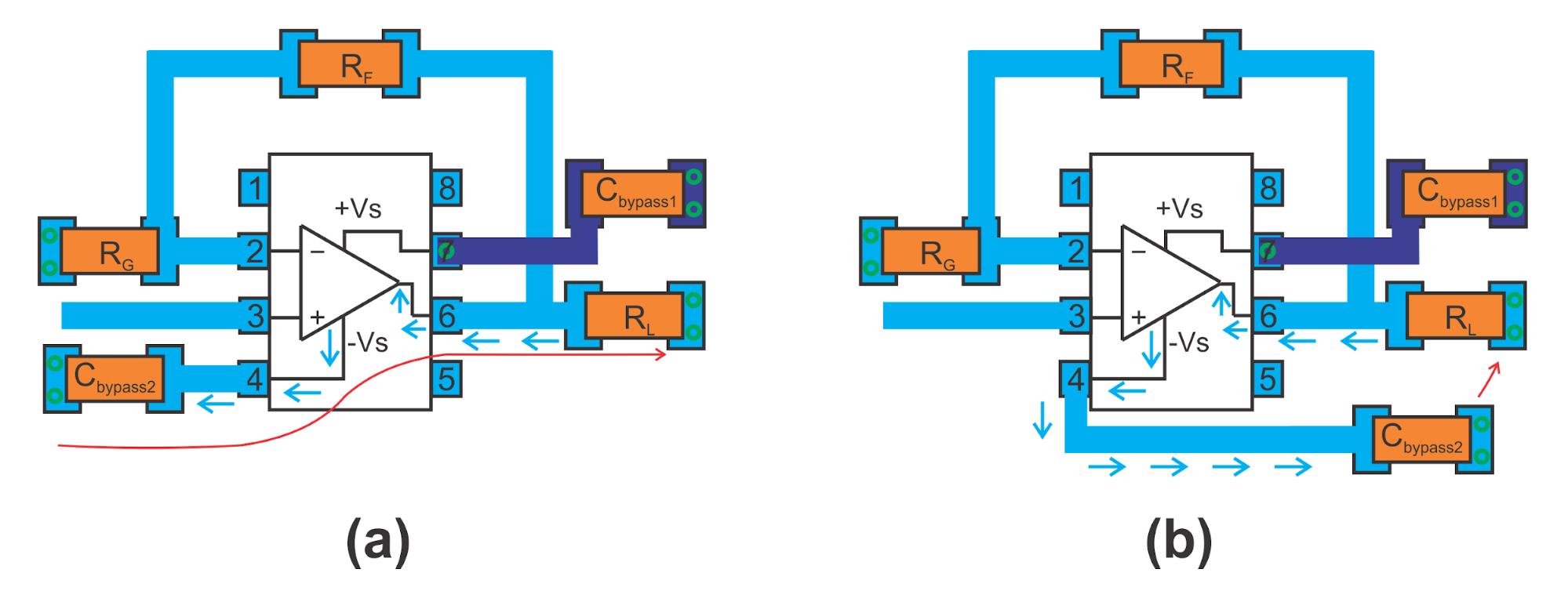

要理解为什么图 2(b) 中的布局表现出较低的失真,请考虑当施加到负载的信号具有负极性时流经接地层的返回电流,即,C 旁路 2 正在提供负载电流。

当输出信号极性为负时,从负载汲取的电流流经顶层迹线和运算放大器电路,如图 3 中的蓝色箭头所示。

图 3. 与图 2 相同的图表,但用蓝色箭头显示电流。

我们知道,高频返回电流直接在信号走线下方流动,以限度地减少环路面积。因此,图 3(a) 中布局的返回电流应该遵循类似于红线所示的路径。

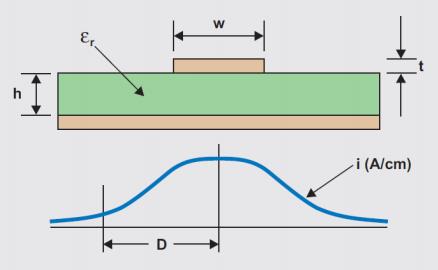

然而,值得注意的是,虽然大部分返回电流直接流过信号走线下方,但它仍然可以在接地平面上稍微扩散,如图 4 所示。

图 4.高频返回电流的分布。图片由Segera Davies提供。

因此,对于图 3(a) 中的布局,返回电流会扰乱运算放大器输入端的电压。耦合到运算放大器输入的误差信号将与信号相关,因此会导致运算放大器输出失真。由于与信号相关的误差电压仅出现在输出电压的一种极性(负极性)期间,它主要会增加二次谐波失真。

在图 3(b) 中,返回电流在地平面上会选择什么路径?

同样,信号迹线正下方的路径(蓝色箭头下方)将提供尽可能低的电感。但是,在这种情况下,旁路电容的接地端非常靠近负载的接地端。因此,与电感的路径相比,3(a) 中红色箭头所示的路径可以提供非常小的电阻。事实上,返回电流会选择阻抗的路径(路径电感和电阻都应考虑)。

为了确定返回电流的准确分布,我们需要模拟工具;但是,我们可以推断出一部分返回电流将流过红色箭头周围,而相对较小的电流将流过蓝色箭头下方。由于在信号迹线下方流动的电流相对较小,我们可以预期在电路的敏感节点下方(运算放大器输入周围)有一个“更安静”的接地。

使旁路电容的接地端远离运算放大器输入端是减少谐波失真的有效技术,不同芯片制造商的不同技术文档中通常推荐这样做。

如果负载远离运算放大器输出怎么办?

让我们再看一个示例,其中负载位于距运算放大器输出一定距离的位置,如图 5 所示。

图 5. 我们的示例运算放大器电路,但负载远离运算放大器输出。

同样,我们应该使旁路电容器的接地端远离运算放大器输入端。电容器应放置在靠近运算放大器电源引脚的位置,其接地端子应靠近运算放大器输出。

返回电流的相当一部分应该遵循上面讨论的低电阻路径,导致下图中红线所示的返回电流路径。

需要适当的去耦才能从高速运算放大器中提取的线性度性能。此外,旁路电容器的接地侧应放置在靠近运算放大器输出并远离其输入的位置,以便我们可以在电路的敏感节点(运算放大器输入周围)下有一个“更安静”的接地。

上一篇:DC-DC动态特性怎么优化改善

下一篇:一种为微控制器供电的低成本方法

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 深度剖析线性稳压器动态调节机制及三端与 LDO 稳压器差异2025/8/12 16:16:19

- 五种常用 UPS 电源并机方案大揭秘2025/8/11 15:56:03

- 电源设计故障防护:现代保护 IC 的简单解决方案2025/8/5 16:10:25

- 电源噪声的来源与应对策略2025/8/4 16:31:13

- 直流可编程电源串联或并联连接的优势2025/8/4 16:25:37