辅助绕组中漏感会使控制器的短路保护电路失效

出处:维库电子市场网 发布于:2023-07-12 16:12:42

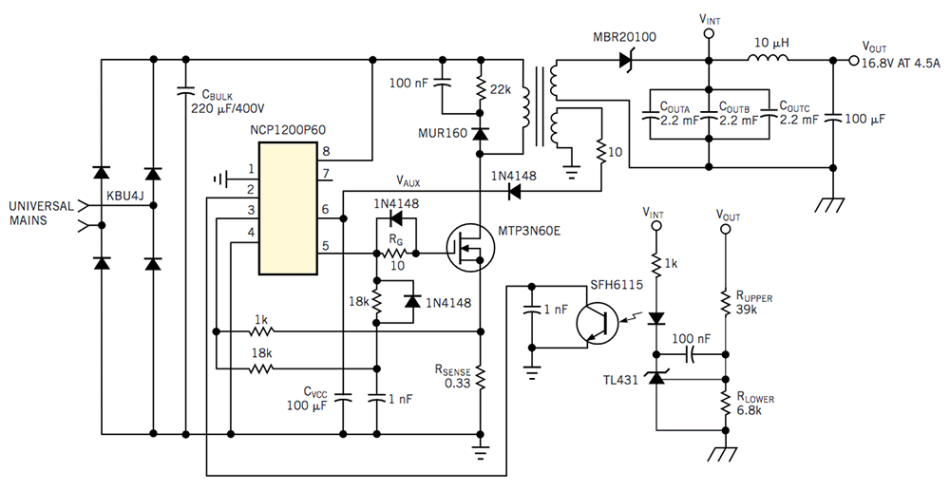

图 1在此电路中,辅助绕组中的漏感会使控制器的短路保护电路失效。

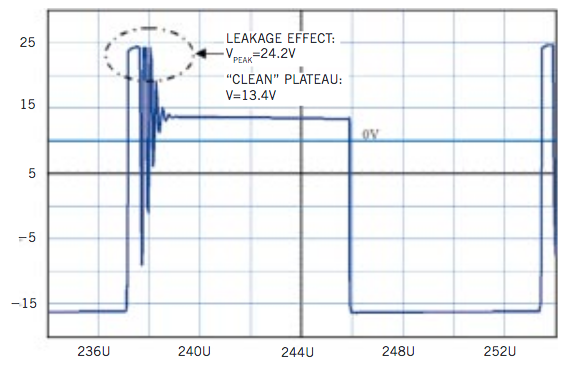

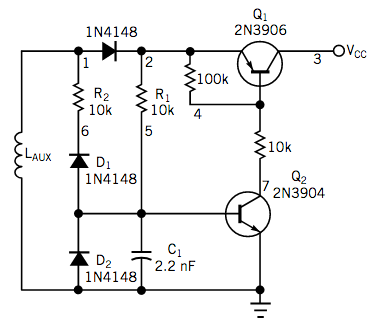

图 2详细说明了输出发生短路时漏感的影响。正如您所看到的,泄漏尖峰将辅助电平推至远高于其常规平台电压,这是您想要获得的值。由于整流二极管充当包络检波器,因此终电压接近 24V,与您预期的 13.4V 相差甚远。因此,如果电平超过控制器数据表中的额定值,则可能存在破坏性情况。您需要使用耗散元件(例如齐纳二极管)来钳位辅助电压。图3显示了为避免漏感问题而采用的电路。组件排列实际上实现了一个独立的采样保持系统。当主电源开关接通时,电容器C 1通过R 2和D 1放电,D 2避免Q 2的基极-发射极结出现大的反向偏压。当主开关打开时,次级电压急剧上升,节点1变为正值。然而,由于C 1放电,Q 1保持开路,并且V CC不增加。

高整流电压图2辅助绕组侧的漏感导致高整流电压。

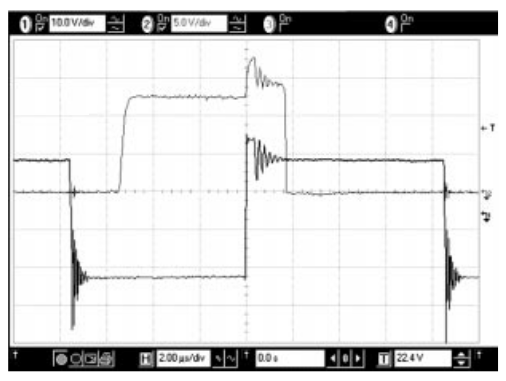

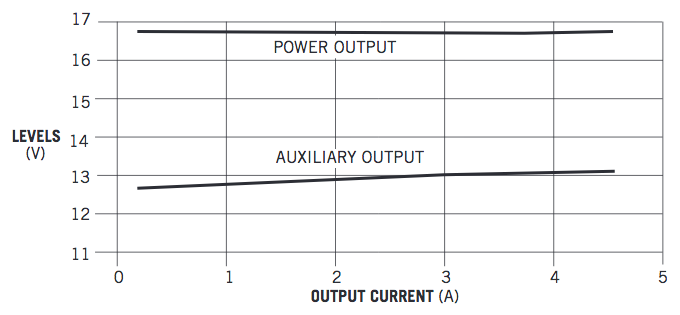

计理念短时间后(可通过 R 1或 C 1调节),Q 2关闭并使 Q 1的基极更接近地面。V CC现在增加并赶上节点 2 处的水平,减去 Q 1的 V CE(SAT)。如果正确选择时间延迟,V CC不会出现任何电压尖峰,因为您已经对平台进行了采样。图 4显示了终结果。在具有低待机功耗的 70W 应用板上执行一些测量,得到如图 5所示的终跟踪结果。您可以看到,I OUT的 4.3A 变化仅导致 V OUT变化 420 mV。您可以在需要电平的初级调节应用中使用该电路,而无需对次级绕组进行大量滤波(从而降低待机模式下的可用辅助能量)或将初级钳位电压降低至更高的耗散值。在NCP1200应用中,当输出出现短路时,辅助绕组正确触发短路保护。

无漏感效应图 4通过延迟采样时间,您可以获得干净的辅助电平,且没有任何漏感效应。

上一篇:FPGA 的电路序列电源

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- AC/DC 与 DC/DC 转换器的工作原理与应用2025/9/26 13:06:39

- 线性稳压电源与开关稳压电源:原理、特性及应用2025/9/17 15:37:35

- 直线电机工作原理与应用全解析2025/9/12 9:44:24

- 详解 BUCK 电路电感额定电流:选型要点与合适数值2025/9/4 16:05:09

- 运算放大器电源电压抑制比(PSRR):关键参数揭秘与电路设计应用2025/9/2 15:29:04