使用 DSP Slice 实现对称 FIR 滤波器

出处:维库电子市场网 发布于:2023-07-21 17:15:58

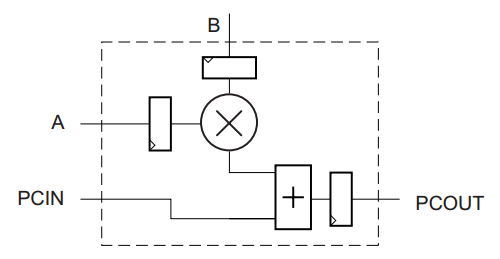

下面的图 6 显示了图 5 的 DSP Slice 的简化框图。

这个简化的框图强调一个切片的输出可以作为输入路由到下一个切片的加法器/减法器。如果我们忽略图 6 中所示的输入寄存器,图 6 的原理图与图 4 虚线框内的电路相同。因此,通过级联这些 DSP 切片,我们可以有效地实现图 4 的 FIR 滤波器。在这种情况下,我们可以使用 FPGA 的通用结构切片来实现红色加法器(参见图 4)。

这里,阴影加法器实现了图 4 中的红色加法器,并且可以使用片内的寄存器来实现延迟线。

上一篇:DSP 中的基本信号操作

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- Microchip 发布PIC16F13145系列MCU,促进可定制逻辑的新发展2024/4/23 15:34:17

- 什么是MCU2024/3/25 17:05:40

- 了解GD32单片机和STM32单片机2024/3/13 14:17:13

- STM32F103单片机概述2024/3/13 14:13:33

- 什么是DSP?DSP的分类2024/1/22 16:38:45