利用片上网络 IP 加速 RISC-V 开发

出处:网络整理 发布于:2023-09-21 15:11:59

近的趋势是广泛采用 RISC-V 内核,这些内核基于开放标准 RISC-V 指令集架构 (ISA) 构建。该系统可通过免版税的开源许可证获得。

在这里,利用片上网络 (NoC) 技术的即插即用功能已成为加速基于 RISC-V 的系统集成的有效策略。这种方法有利于处理器内核或集群与来自多个供应商的知识产权 (IP) 块之间的无缝连接。

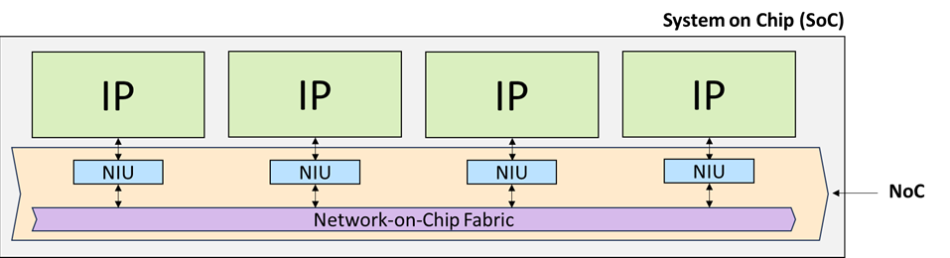

使用 NoC 互连 IP 具有多种优势。NoC 可以扩展到整个设备,每个 IP 都有一个或多个跨越整个 SoC 的接口。这些接口具有自己的数据宽度,以不同的时钟频率运行,并利用 SoC 设计人员常用的 OCP、APB、AHB、AXI、STBus 和 DTL 等多种协议。这些接口中的每一个都链接到相应的网络接口单元(NIU),也称为套接字。

NIU 的作用是从传输 IP 接收数据,然后将这些数据组织并序列化为适合网络传输的标准化格式。多个数据包可以同时传输。到达目的地后,关联的套接字会在将数据呈现给相关 IP 之前通过反序列化和撤消打包来执行相反的操作。此过程是根据链接到该特定 IP 的协议和接口规范来完成的。

IP 块的简单说明可以可视化为实体逻辑块。此外,SoC 通常使用单个 NoC。图 1展示了基本的 NoC 配置。

NoC本身可以使用多种拓扑来实现,包括1D星形、1D环形、1D树形、2D网状、2D环面和全网状,如图2所示。

一些 SoC 设计团队可能希望开发自己专有的 NoC,这是一个资源和时间密集型的过程。这种方法需要由多名工程师组成的团队工作两年或更长时间。使事情变得更具挑战性的是,设计人员通常投入与整个设计的其余部分几乎一样多的时间来调试和验证内部开发的 NoC。

随着设计周期的缩短和收入压力的增加,SoC 开发团队正在考虑商用 NoC IP。该 IP 支持内部开发的 NoC IP 所需的定制,但也可以从第三方供应商处获得。

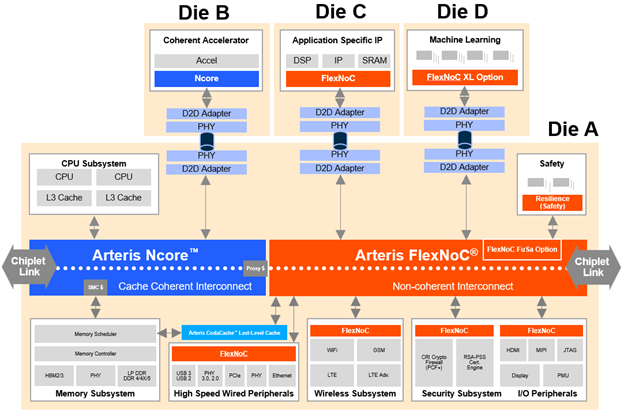

SoC 复杂性不断增长的另一个挑战是在单个设备中使用多个 NoC 和各种 NoC 拓扑(图 3)。例如,芯片的一个部分可能采用分层树形拓扑,而另一部分可能选择 2D 网格配置。

在许多情况下,当今 SoC 中的 IP 模块相当于几年前的整个 SoC,使其成为子系统。因此,这些子系统块的创建者通常会选择采用第三方供应商提供的行业标准 NoC IP。

在需要高水平可定制性以及计算和数据传输协同优化的情况下,例如处理器集群或神经网络加速器,IP 开发团队可能会选择传输机制的自定义实现。或者,他们可能决定利用一种较少采用的、高度化的协议来实现他们的设计目标。

RISC-V 和 NoC集成

对于独立的 RISC-V 处理器内核,这些 IP 可为不需要一致性的设计人员提供 AXI 接口,为需要一致性的设计人员提供 CHI 接口。这使得这些内核能够在 SoC 级别与行业标准 NoC 进行即插即用。

同样,如果设计团队在 RISC-V 设计中选择一种不太常用的集群间通信协议,则该集群还可以具有面向外部连接的 ACE、AXI 或 CHI 接口。此方法允许快速连接到 SoC 的 NoC。

下面的图 4显示了非一致性和缓存一致性选项。除了在 IP 和 SoC 中使用之外,这些 NoC 还可以在多芯片系统中充当超级 NoC。

业界正在经历以基于开放标准 RISC-V 指令集架构的处理器内核和集群为特色的 SoC 设计的急剧增长。

通过利用 NoC 技术提供的即插即用功能,可以加速基于 RISC-V 的系统(包括多芯片系统)的开发和采用。这使得 RISC-V 处理器内核或集群与多个供应商提供的 IP 功能块之间能够实现快速、无缝和高效的连接。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- CAN XL 通信技术在车载毫米波雷达中的应用 (2)2025/8/8 16:24:00

- 光纤线和网线有啥区别2025/8/7 17:21:57

- 网线怎么排2025/8/1 11:42:44

- 全面对比:光纤线与网线的差异大揭秘2025/7/30 17:00:38

- SPI 通信协议的基本概念和工作模式2025/7/30 16:53:59